Innehållsförteckning:

- Författare John Day day@howwhatproduce.com.

- Public 2024-01-30 12:46.

- Senast ändrad 2025-01-23 15:11.

Det här är en handledning om hur du bygger ett stoppur på en minut med VHDL och ett Basys 3 -kort. En sådan enhet är idealisk för spel där varje spelare har högst en minut på sig att göra sitt drag. Stoppuret visar exakt sekunder och millisekunder på sjusegmentsdisplayen, från 0 sekunder och 0 millisekunder, upp till 60 sekunder och 0 millisekunder. Två knappar används också: den centrala knappen, som används för att starta, stoppa och fortsätta timern, och den högra knappen, som används för att starta om timern. När enheten jämförs sida vid sida med den inbyggda stoppuret på en smart telefon märks klockans noggrannhet.

Steg 1: Skaffa hårdvara/programvara

1. Basys 3 Artix-7 FPGA Trainer Board från Digilent med Micro-USB till USB-kabel

2. Vivado 2016.2 Design Suite från Xilinx

Steg 2: Block Diagram

Denna krets är konstruerad beteendemässigt och använder inbyggda Xilinx-komponenter, men kan också beskrivas strukturellt, vilket framgår av det allmänna strukturdiagrammet ovan. Av diagrammet kan man se att kretsen drivs av två frekvensdelare. En av frekvensdelarna körs på 1 centisekund och driver katodräknaren som används som siffrorna som visas på sjusegmentsdisplayen. Den andra frekvensdelaren körs på 240Hz och används för att driva anodräknaren som roterar genom anoderna så att alla siffror visas korrekt på sjusegmentsdisplayen. Kodaren tar katodlogiken från katodräknaren och anodlogiken från anodräknaren och kodar den till utgångens katod och anod som kör sjusegmentsdisplayen. Funktionen för denna kodare är att katodutgången ändras varje gång anodutgången ändras. Katodutgången kan inte köras oberoende av räknaren eftersom anoderna måste rotera genom de fyra separata siffrorna.

Steg 3: Projektmodul

För det första görs ett processblock för CEN så att när en knapptryckning upptäcks växlar ENABLE. Detta fungerar som stopp/start av katodräknaren.

I nästa processblock ställs centisekund- och 240Hz -klocksignalerna så att deras respektive räknare ökar med 1 varje gång den interna 100mHz -klockan når en stigande kant. När centisekundräknaren når 500000, återställs den till 0. Samtidigt skulle 240Hz -räknaren återställas när räkningen når 41667.

För katodsektionen i koden, om ENABLE är '0', kommer katodräkningen att pausas. Om återställningsknappen trycks in under denna tid återställs alla räkningar till "0000". Samtidigt, om ENABLE är '1', fortsätter katodräkningen tills katodräkningen når 60,00, där den utlöser stoppsignalen till '1'. Stoppsignalen leder tillbaka till CEN -processblocket och gör att ENABLE är '0' medan stoppsignalen är '1' och ändras inte förrän återställningsknappen trycks in.

Slutligen konfigureras sju segmentdisplayen genom att ha de 4 anoderna korrekt anslutna till var och en av deras 8 katoder för att visa sina respektive siffror 0-9 samtidigt.

Steg 4: Begränsningar

Denna begränsningsfil ansluter de angivna in- och utgångarna från VHDL till de nödvändiga, fysiska delarna av Basys -kortet. För detta projekt innehåller komponenterna de fyra anoderna och var och en av deras åtta katoder för displayen med sju segment, den interna 100 mHz -klockan, mittknappen och den högra knappen.

Steg 5: Testa

När du har fyllt i koden kan du nu programmera FPGA via USB -kabeln. Displayen med sju segment ska visa 0,00. Testa om knapparna fungerar genom att trycka på mittknappen för att starta timern tills den når 60,00 och stannar; när som helst däremellan kan du trycka på den centrala knappen igen för att pausa den. När den har pausats kan du trycka på höger knapp för att återställa timern till 0,00. Om allt fungerar korrekt, grattis till att du precis har byggt en minuts timer!

Rekommenderad:

Arduino Leonardo stoppur: 3 steg

Arduino Leonardo Stoppur: Kredit: https://www.instructables.com/id/Arduino-Stopwatch … Denna stoppurskonstruktion härstammar från länken ovan, som är ett stoppur som räknas från 1, medan den här räknar ner från 60 sekunder . Det mesta av koden jag har använt följer originalet

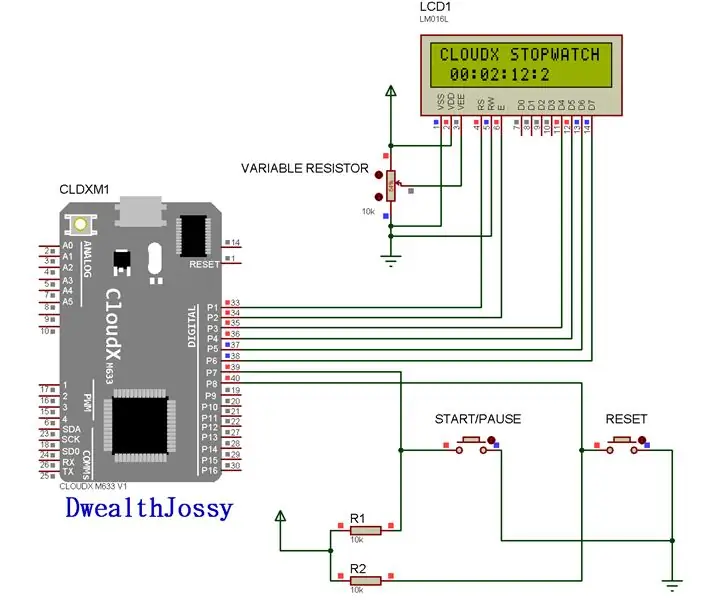

Enkelt CloudX M633 digitalt stoppur: 4 steg

Enkelt CloudX M633 digitalt stoppur: I det här projektet kommer vi att göra en version av en digital klocka som kan registrera timmar, minuter och sekunder, precis som ett stoppur på din mobiltelefon! Vi ska använda en LCD för att visa tiden

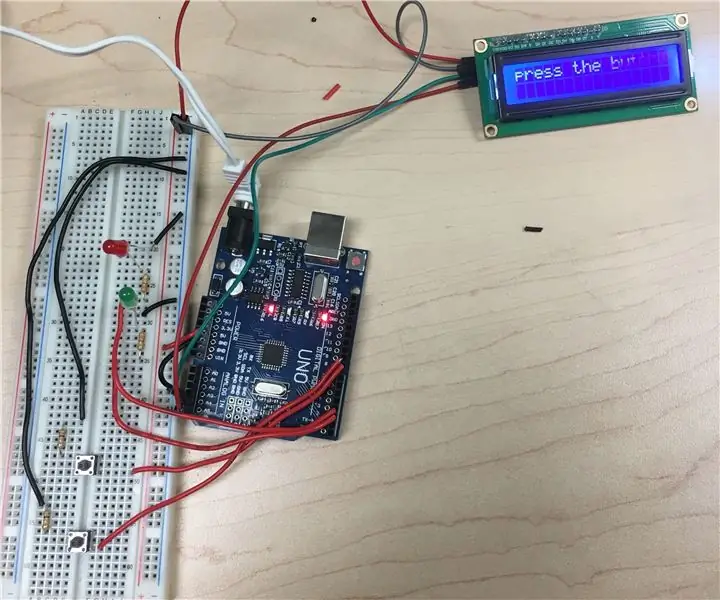

Arduino stoppur med I2C LCD: 5 steg

Arduino stoppur med I2C LCD: I det här projektet kommer jag att lära dig att använda en LCD -skärm och en Arduino som ett interaktivt stoppur. När ditt projekt är klart med den angivna koden ska det se ut som på bilden ovan. Gå till nästa steg för att lära dig var du ska börja

Grundläggande stoppur med VHDL och Basys3 Board: 9 steg

Grundläggande stoppur med VHDL- och Basys3 -kort: Välkommen till instruktionen om hur man bygger ett stoppur med grundläggande VHDL- och Basys 3 -kort. Vi är glada att kunna dela vårt projekt med dig! Detta var ett slutprojekt för kurs CPE 133 (Digital Design) på Cal Poly, SLO hösten 2016. Projektet vi byggde

VHDL -stoppur: 8 steg (med bilder)

VHDL-stoppur: Detta är en handledning om hur man gör ett stoppur med VHDL och ett FPGA-kretskort, som ett Basys3 Atrix-7-kort. Stoppuret kan räkna från 00.00 sekunder till 99.99 sekunder. Den använder två knappar, en för start/stopp -knappen och en för