Innehållsförteckning:

- Författare John Day day@howwhatproduce.com.

- Public 2024-01-30 12:46.

- Senast ändrad 2025-01-23 15:11.

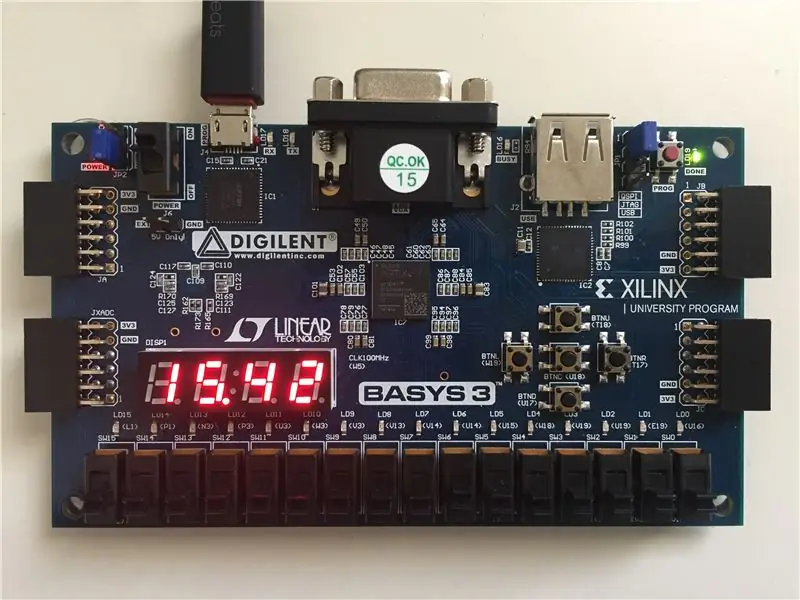

Detta är en handledning om hur du gör ett stoppur med VHDL och ett FPGA-kretskort, som ett Basys3 Atrix-7-kort. Stoppuret kan räkna från 00.00 sekunder till 99.99 sekunder. Den använder två knappar, en för start/stopp -knappen och en annan för återställningsknappen. Siffrorna visas på tavlan med sju segment med dess anoder och katoder. Det finns tre olika filer som behövs för att få detta stoppur att fungera.

Steg 1: Hårdvara/programvara

- Basys3 Atrix-7 FPGA Board

- Vivado Design Suite från Xilinx

- USB 2.0 A-hane till Micro-B-hane

Steg 2: Block Diagram

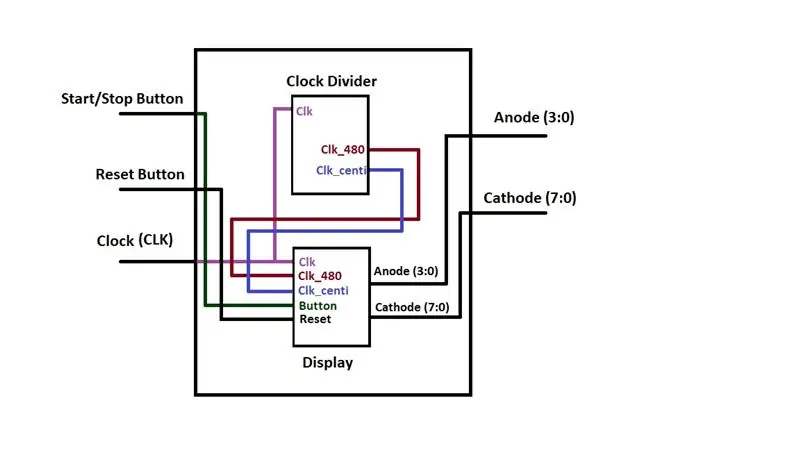

Det övergripande stoppuret har tre ingångar och två utgångar. De tre ingångarna är start/stopp, återställning och klocka. Start/stopp och återställning är knappar och klockan är styrelsens 100MHz klocka. De två utgångarna är anoder och katoder för sjusegmentsdisplayen.

Den första modulen (klockdelare) har en ingång och två utgångar. Ingången är styrelsens 100MHz klocka och utgångarna är två separata klockor, en som körs på 480Hz och en annan som kör 0,5MHz.

Den andra modulen (displayen) har fem ingångar och två utgångar. Ingångarna är kortets 100MHz -klocka, de två klockorna från klockavdelningsmodulen och start/stopp- och återställningsknapparna. Utgångarna är anoder och katoder.

Den sista modulen (modellerad av hela blockschemat) har tre ingångar och två utgångar. Det här är filen som sammanför allt. Ingångarna är kortets 100MHz och knapparna start/stopp och återställning. Utgångarna är anoder och katoder som styr displayen med sju segment. Alla in- och utgångar finns fysiskt på kortet för den sista modulen.

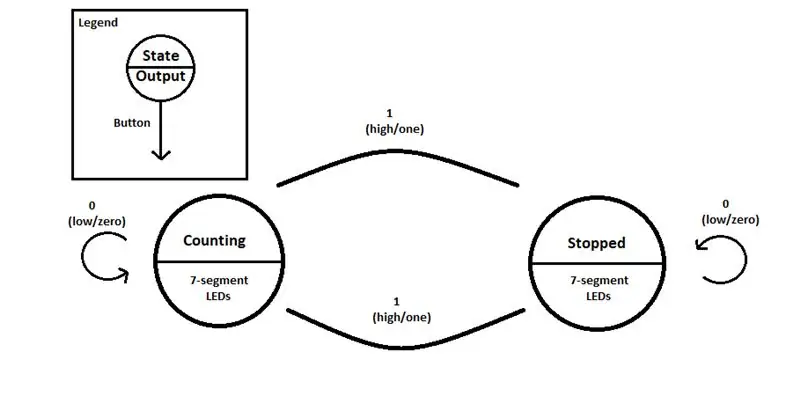

Steg 3: Ange diagram

Bilden ovan visar tillståndsdiagrammet för hur stoppuret fungerar. Att trycka på återställningsknappen har ingen inverkan på stoppurets tillstånd. Nästa tillstånd bestäms av start/stopp -knappen. Starten/stoppet är "HIGH" när det hålls nedtryckt, men inte när det hålls nedtryckt och "LOW" när knappen har slagit tillbaka eller hålls nere efter att ha varit "HIGH" en stund.

Om stoppuret räknar och start/stopp -knappen går "HÖG", slutar det att räkna. Om stoppuret är stoppat och start/stopp -knappen går "HIGH" börjar det räkna igen. För båda delstaterna, om start/stopp -knappen är "LÅG", kommer den att förbli i det tillstånd som den är för närvarande.

Steg 4: Clock Divider Module

Klockavdelningsmodulen har en ingång, kortets 100MHz klocka och två utgångar, 480Hz och 0.5MHz klockorna. 480Hz-klockan används för att hålla alla lysdioder på sjusegmentsdisplayen "på" samtidigt genom att snabbt växla igenom de fyra. 0,5 MHz-klockan används för att stoppuret faktiskt ska räknas med centisekunder.

Steg 5: Displaymodul

Denna displaymodul har fem ingångar, kortets 100MHz klocka, de två klockorna från klockmodulen och start/stopp och återställningsknapparna, och två utgångar, anoder och katoder. Denna modul har också "logiken" för hur stoppuret räknas och inkorporerar finite state -maskinen.

Steg 6: Bindningsmodul

Denna sista modul är den som för samman de två andra modulerna. Den har tre ingångar, kortets 100MHz klocka och start/stopp och återställningsknappar, och två utgångar, anoder och katoder. 100MHz -klockan går till klockavdelningsmodulen och displaymodulen, och start/stopp- och återställningsknapparna går till displaymodulen. Klockavdelningsmodulens utgångar (480Hz och 0,5MHz) går till de två klockingångarna på displaymodulen. Utgångarna från displaymodulen (anoder och katoder) går till den sista modulens utgångar.

Steg 7: Begränsningar

De två ingångarna kan vara valfria knappar på Basys3 Atrix-7 FPGA-kortet och utgångarna kommer att vara de fyra anoderna och de åtta katoderna (eftersom du också vill ha en decimalpunkt mellan sekunder och millisekunder) för sjusegmentsdisplayen.

Steg 8: Klar

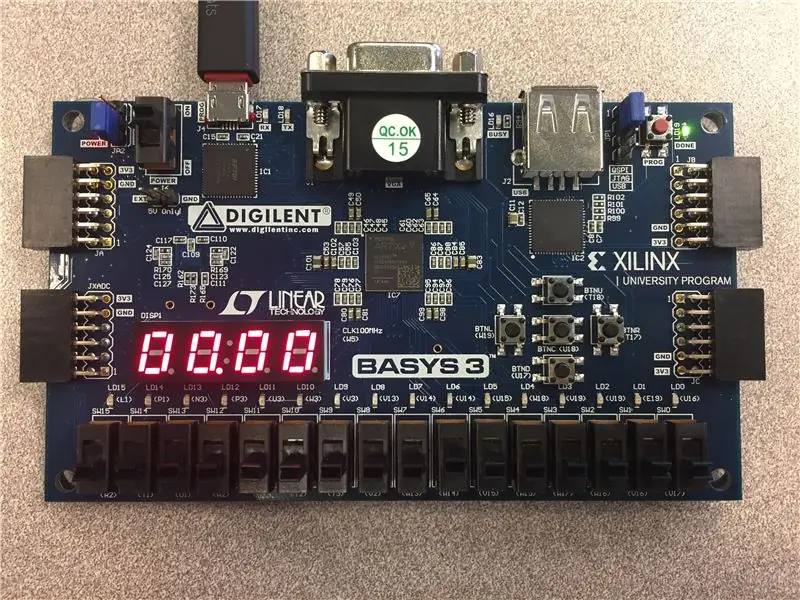

Ladda upp programmet till ditt Basys3 Atrix-7 FPGA-kort och tryck på start/stopp-knappen för att få stoppuret igång!

Rekommenderad:

Ta fantastiska bilder med en iPhone: 9 steg (med bilder)

Ta fantastiska bilder med en iPhone: De flesta av oss har en smartphone med oss överallt nuförtiden, så det är viktigt att veta hur du använder din smartphone -kamera för att ta fantastiska bilder! Jag har bara haft en smartphone i ett par år, och jag har älskat att ha en bra kamera för att dokumentera saker jag

Hur: Installera Raspberry PI 4 Headless (VNC) med Rpi-imager och bilder: 7 steg (med bilder)

Hur: Installera Raspberry PI 4 Headless (VNC) med Rpi-imager och bilder: Jag planerar att använda denna Rapsberry PI i ett gäng roliga projekt tillbaka i min blogg. Kolla gärna in det. Jag ville börja använda mitt Raspberry PI men jag hade inte ett tangentbord eller en mus på min nya plats. Det var ett tag sedan jag installerade en hallon

Cordisk algoritm med VHDL: 4 steg

Cordisk algoritm med VHDL: ## Detta är den mest klickade, populära länken i Google för VHDL -implementering av CORDIC ALGORITHM för att generera sinus- och cosinusvåg ## För närvarande finns det många hårdvarueffektiva algoritmer, men dessa är inte välkända på grund av softwarens dominans

Hur man tar isär en dator med enkla steg och bilder: 13 steg (med bilder)

Hur man tar isär en dator med enkla steg och bilder: Detta är en instruktion om hur man demonterar en dator. De flesta av de grundläggande komponenterna är modulära och lätt att ta bort. Det är dock viktigt att du är organiserad kring det. Detta hjälper dig att inte förlora delar, och även för att göra ommonteringen

Videobearbetning med VHDL och en Zybo: 10 steg

Videobearbetning med VHDL och en Zybo: FPGA är snabbare än processorer att bearbeta, eftersom de kan göra många beräkningar parallellt Obs! Detta projekt är fortfarande under uppbyggnad och kommer att förbättras (så snart jag har tid). Samtidigt reser jag jorden runt