Innehållsförteckning:

- Författare John Day day@howwhatproduce.com.

- Public 2024-01-30 12:45.

- Senast ändrad 2025-01-23 15:11.

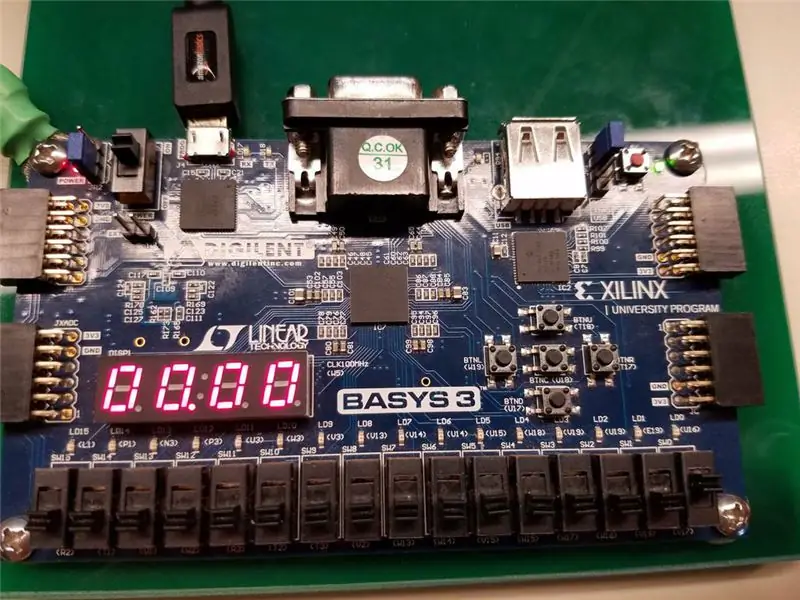

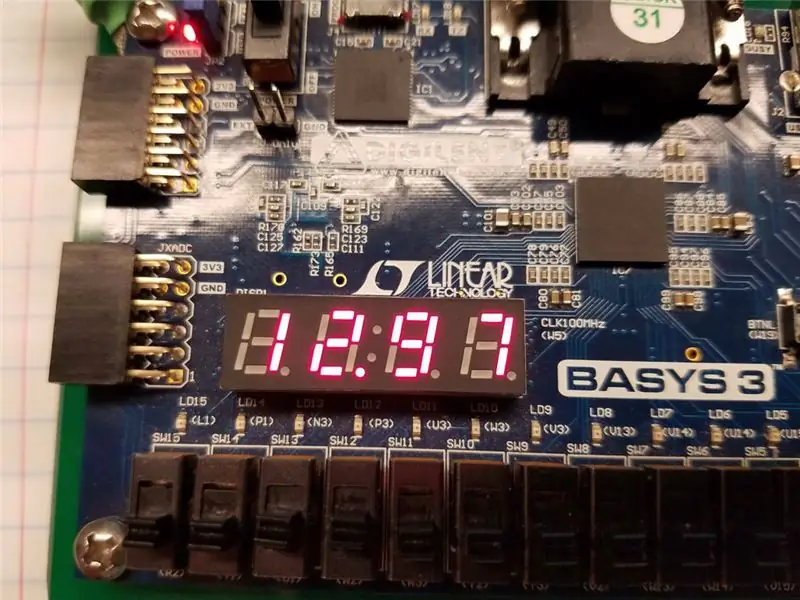

Välkommen till instruktionen om hur man bygger ett stoppur med grundläggande VHDL och Basys 3 -kort. Vi är glada att kunna dela vårt projekt med dig! Detta var ett slutprojekt för kurs CPE 133 (Digital Design) på Cal Poly, SLO hösten 2016. Projektet vi byggde är ett enkelt stoppur som startar, återställer och pausar tid. Den tar in tre tryckknappar på Basys3-kortet som ingångar, och tiden visas på kortets fyrsiffriga sjusegmentsdisplay. Den förflutna tiden visas i formatet sekunder: centisekunder. Den använder kortets systemklocka som en ingång för att hålla reda på den förflutna tiden och matar ut tiden till de fyra siffrorna i sjusegmentsdisplayen.

Steg 1: Material

Materialet du behöver för detta projekt:

- 1 dator med Vivado Design Suite WebPack installerat från Xilinx (föredrar version 2016.2)

- 1 Digilent Basys3 Xilinx Artix-7 FPGA-kort

- 1 USB -portkabel

Steg 2: Ställa in och utgångar

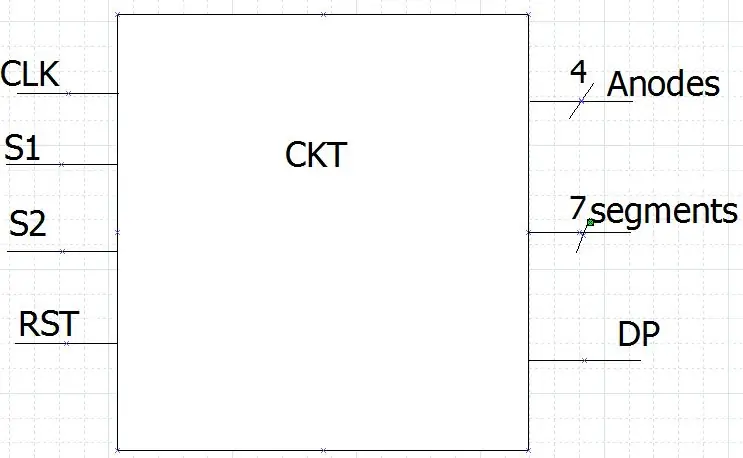

Figuren ovan visar ett blockdiagram över huvudnivån för huvudurens urklockmodul. Stoppuret tar in ingångar "CLK" (klocka), "S1" (startknapp), "S2" (pausknapp) och "RST" (återställning) och har en 4-bitars utgång "Anoder", en 7-bitars utgång utmatningssegment och en enda bitars utgång "DP" (decimalpunkt). När ingången "S1" är hög börjar stoppuret räkna tid. När "S2" är låg pausar stoppuret tiden. När "RST" är hög, stoppar stoppuret och återställer tiden. Det finns fyra delmoduler i kretsen: klockavdelaren, sifferräknaren, sju-segmentdisplaydrivrutinen och sjusegmentskodaren. Stoppurets huvudmodul kopplar ihop alla delmoduler och till ingångar och utgångar.

Steg 3: Gör klockor

Klockavdelningsmodulen tar in en systemklocka och använder en divisoringång för att skapa en klocka med valfri hastighet som inte är större än systemklockans. Stoppuret använder två olika klockmoduler, en som skapar en 500 Hz klocka och en annan som skapar en 100 Hz klocka. Schemat för klockavdelaren visas i figuren ovan. Klockavdelaren tar in en en-bitars ingång "CLK" och en 32-bitars ingång "Divisor" och en-bitars utgången "CLKOUT". "CLK" är systemklockan och "CLKOUT" är den resulterande klockan. Modulen innehåller också en NOT -grind, som växlar signalen "CLKTOG" när räkningen når värdet på avdelaren.

Steg 4: Räkna till tio

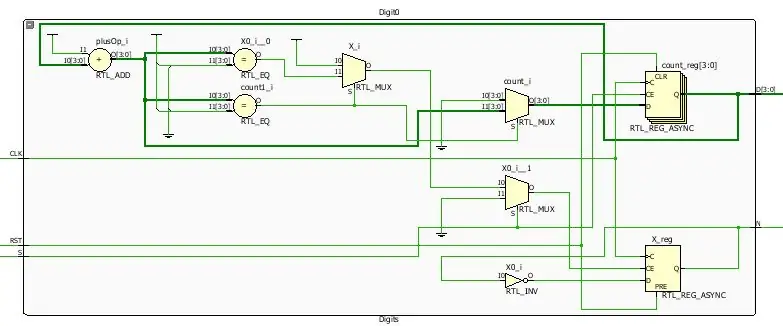

Siffräknaren räknar varje siffra från 0 till 10 och skapar en annan klocka för nästa siffra att fungera från den oscillerar när räkningen når 10. Modulen tar in tre enkelbitsingångar "S", "RST" och "CLK "och resulterar i en enda bitars utgång" N "och en 4-bitars utgång" D ". Ingång "S" är aktiveringen i ingången. Klockan slås på när "S" är högt och avstängt när "S" är lågt. "RST" är återställningsingången så att klockan återställs när "RST" är hög. "CLK" är klockingången för sifferräknaren. "N" är klockutgången som blir ingångsklockan för nästa siffra. Utgång "D" presenterar det binära värdet för den siffra som räknaren är på.

Steg 5: Visa nummer

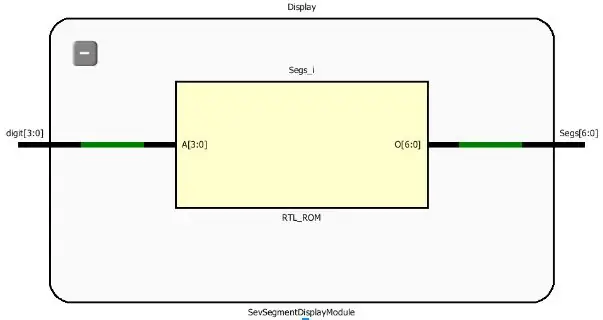

Den sju-segmentiga skärmkodaren kommer att koda det binära numret som tas emot från sju-segmentdisplaydrivarmodulen och förvandla den till en ström av bitar som kommer att tolkas som "1" eller "0" -värden för varje segment av displayen. Det binära talet tas emot av modulen som 4-bitars ingång "siffra" och resulterar i 7-bitars utmatning "segment". Modulen består av ett enda fallprocessblock som tilldelar en specifik 7-bitars ström för varje möjligt ingångsvärde från 0 till 9. Varje bit i sjubitsströmmarna representerar ett av de sju segmenten av siffrorna på displayen. Ordningen på segmenten i strömmen är "abcdefg" med "0: er" som representerar segmenten som lyser upp för det givna numret.

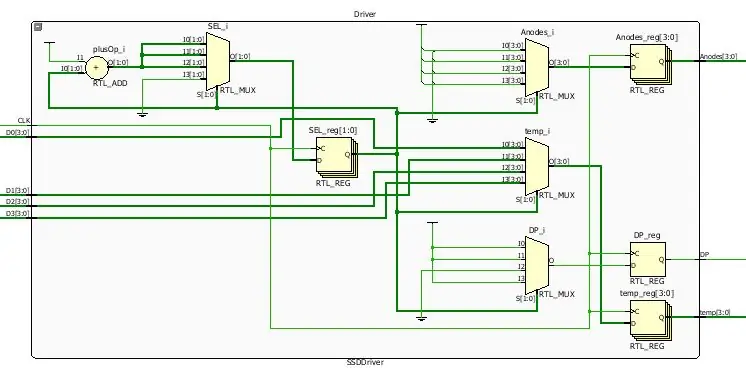

Steg 6: Hur man visar stoppuret

I sju-segment display-drivrutinsmodulen finns fyra 4-bitars ingångar "D0", "D1", "D2" och "D3", var och en representerar de fyra siffror som ska visas. Ingång "CLK" är systemets klocksignal. En-bitars utgång "DP" representerar decimalpunkten på sjusegmentsdisplayen. 4-bitars utgången "Anoder" bestämmer vilken siffra på sjusegmentsdisplayen och 4-bitars utgång "temp" beror på tillståndet för 2-bitars kontrollingången "SEL". Modulen använder 4 multiplexrar för styringången "SEL" och de tre utgångarna; "Anoder", "temp" och "DP".

Steg 7: Samla allt

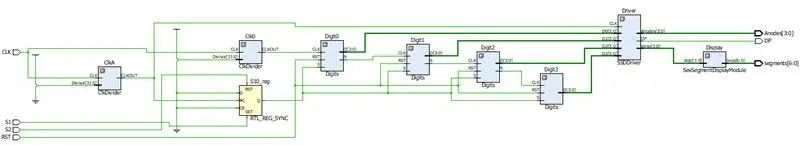

Ett 'om' processblock som körs av 500Hz -klockan används för att skapa start- och pausknapparna. Koppla sedan ihop alla delmoduler i stoppurets huvudmodul genom att deklarera komponenterna i varje enskild delmodul och använda olika signaler. Siffermodulerna tar in klockutgången från den föregående siffrans submodul med den första som tar in 100Hz -klockan. "D" -utgångarna från siffrans submoduler blir sedan "D" -ingångarna för sju segment display -drivrutinsmodulen. Och slutligen blir "temp" -utgången från sju segments display -drivrutinsmodulen "temp" -ingång för sju segmentskodningsmodulen.

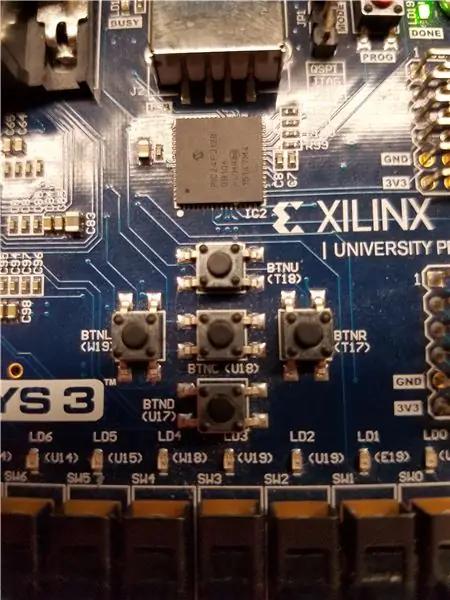

Steg 8: Begränsningar

Använd 3 tryckknappar (W19, T17 och U18) för ingångar "RST", "S1" och "S2". W19 är återställningsknappen, T17 är startknappen (S1) och U18 är pausknappen (S2). En begränsning för klockingångsinmatningen krävs också med port W5. Kom också ihåg att lägga till den här raden i klockbegränsningen:

create_clock -add -name sys_clk_pin -period 10.00 -vågform {0 5} [get_ports {CLK}]

Länka också anoderna och segmenten till kortet så att stoppuret visas på sjusegmentsdisplayen som visas i begränsningsfilen.

Steg 9: Testning

Se till att din enhet fungerar genom att spela med de tre knapparna: tryck och håll dem i varje möjlig ordning för att hitta eventuella problem med din kod.

Rekommenderad:

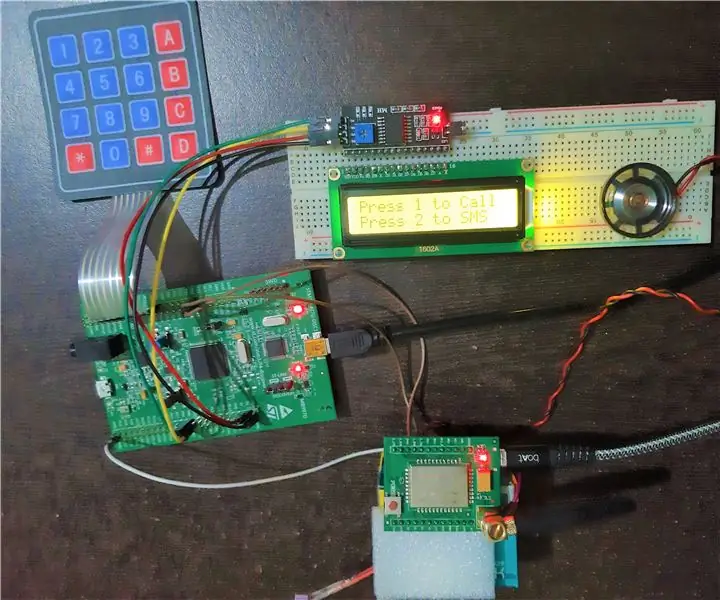

Grundläggande mobiltelefon med STM32F407 Discovery Kit och GSM A6 -modul: 14 steg (med bilder)

Grundläggande mobiltelefon med STM32F407 Discovery Kit och GSM A6 -modul: Har du någonsin velat skapa ett coolt inbäddat projekt ?. Om ja, vad sägs om att bygga en av de mest populära och allas favoritprylar, dvs mobiltelefon !!!. I denna instruktionsbok kommer jag att guida dig om hur du bygger en grundläggande mobiltelefon med STM

8 Reläkontroll med NodeMCU och IR -mottagare med WiFi och IR -fjärrkontroll och Android -app: 5 steg (med bilder)

8 Reläkontroll med NodeMCU och IR -mottagare med WiFi och IR -fjärrkontroll och Android -app: Styrning av 8 reläväxlar med nodemcu och IR -mottagare via wifi och IR -fjärrkontroll och Android -app. Fjärrkontrollen fungerar oberoende av wifi -anslutning. HÄR ÄR EN UPPDATERAD VERSIONKLICK HÄR

VHDL En minuts stoppur: 5 steg

VHDL One Minute Stopwatch: Detta är en handledning om hur man bygger ett stoppur på en minut med VHDL och ett Basys 3 -kort. En sådan enhet är idealisk för spel där varje spelare har högst en minut på sig att göra sitt drag. Stoppuret visar exakt sekunder och millisekunder

VHDL -stoppur: 8 steg (med bilder)

VHDL-stoppur: Detta är en handledning om hur man gör ett stoppur med VHDL och ett FPGA-kretskort, som ett Basys3 Atrix-7-kort. Stoppuret kan räkna från 00.00 sekunder till 99.99 sekunder. Den använder två knappar, en för start/stopp -knappen och en för

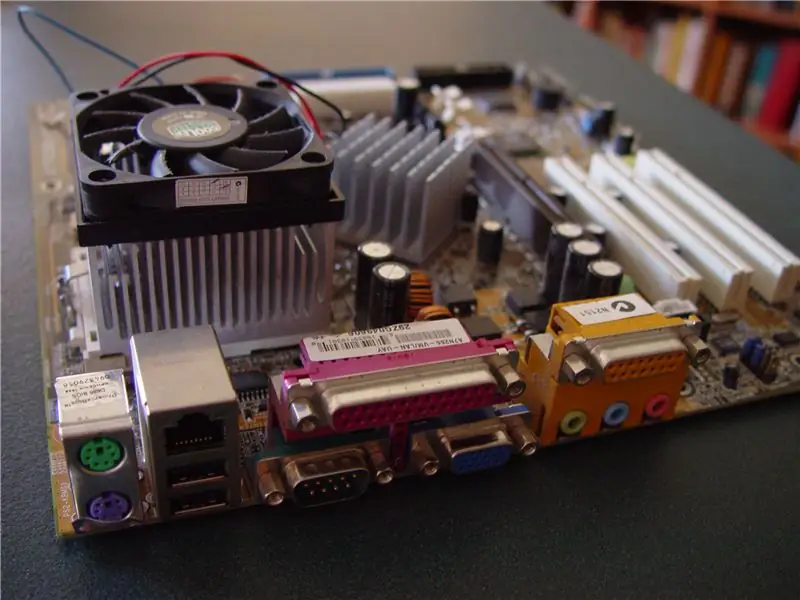

Reparera grundläggande datorhårdvaruproblem (systemdiskfel och trasig nätaggregat och saknade/korrupta filer): 4 steg

Reparera grundläggande datorhårdvaruproblem (systemdiskfel och trasig PSU och filer som saknas/är korrupta): DENNA GUIDE ÄR INTE SLUTAD, TILLÄGGER JAG MER INFORMATION NÄR JAG FÅR EN CHANS.Om du behöver hjälp med att fixa en dator eller om du har några frågor överhuvudtaget, meddela mig " I den här instruktören kommer jag att berätta hur du reparerar grundläggande kom