Innehållsförteckning:

- Steg 1: Vad är Vivado HLS?

- Steg 2: HLS videobibliotek

- Steg 3: Syntetisera

- Steg 4: Versionering och annan information för export

- Steg 5: Exportera till ett Vivado IP -bibliotek

- Steg 6: Syntes- och exportanalys

- Steg 7: Lägga till IP -biblioteket i Vivado

- Steg 8: Uppgradera

- Steg 9: Ytterligare detaljer och information

- Steg 10: Utmatning och inmatning

- Steg 11: AXI -registergränssnitt

- Steg 12: Dataflow Pragma

- Författare John Day day@howwhatproduce.com.

- Public 2024-01-30 12:46.

- Senast ändrad 2025-01-23 15:11.

Har du någonsin velat bearbeta i realtid på video utan att lägga till mycket latens eller i ett inbäddat system? FPGA (Field Programmable Gate Arrays) används ibland för att göra detta; Men att skriva videobearbetningsalgoritmer på hårdvaruspecifikationsspråk som VHDL eller Verilog är i bästa fall frustrerande. Ange Vivado HLS, Xilinx -verktyget som låter dig programmera i en C ++ - miljö och generera hårdvaruspecifikationens språkkod från den.

Obligatoriska program:

- Vivado HLS

- Vivado

- (Om du använder AXI -registren) Vivado SDK

(Valfritt) Ladda ner Xilinx -exemplen här:

Xilinx HLS -videoexempel

Steg 1: Vad är Vivado HLS?

Vivado HLS är ett verktyg som används för att förvandla c ++ - liknande kod till hårdvarustrukturer som kan implementeras på en FPGA. Den innehåller en IDE för att göra denna utveckling. När du har slutfört din utveckling av koden för HLS kan du exportera din genererade IP i ett format för användning med Vivado.

Ladda ner de bifogade filerna och lägg dem nära där du ska skapa ditt projekt. (byt namn på dem igen till "top.cpp" och "top.h" om de har ett randomiserat namn)

Steg 2: HLS videobibliotek

HLS -videobiblioteket har dokumentation med referensdesigner i detta dokument: XAPP1167 En annan bra resurs är Xilinx Wiki -sidan om det.

Starta Vivado HLS.

Skapa ett nytt projekt.

Ta filerna som du laddade ner i föregående steg och lägg till dem som källfiler. (Obs! Filerna kopieras inte till projektet, utan förblir istället där de är)

Använd sedan Bläddra -knappen för att välja den översta funktionen.

På nästa sida väljer du den Xilinx -del du använder.

Steg 3: Syntetisera

Lösning => Kör C -syntes => Aktiv lösning

Efter ~ 227.218 sekunder bör det göras. (Obs: din faktiska syntestid varierar beroende på många faktorer)

Steg 4: Versionering och annan information för export

Versionsnummer interagerar med Vivado för att du ska kunna uppdatera IP: n i en design. Om det är en mindre versionändring kan det göras på plats medan större versionändringar kräver att du manuellt lägger till i det nya blocket och tar bort det gamla. Om dina gränssnitt inte har ändrats och versionsuppdateringen är en mindre kan uppdateringen görs helt automatiskt genom att trycka på uppdateringens IP -knapp. Du kan köra "report_ip_status" i Vivado tcl -konsolen för att se status för din IP.

Ställ in versionsnummer och annan information i Lösning => Lösningsinställningar …

Alternativt kan dessa inställningar ställas in under exporten.

Steg 5: Exportera till ett Vivado IP -bibliotek

Lösning => Exportera RTL

Om du inte ställde in IP -bibliotekets detaljer i föregående steg kan du göra det nu.

Steg 6: Syntes- och exportanalys

På den här skärmen kan vi se statistiken om vår exporterade modul som visar att den uppfyller vår klockperiod på 10ns (100MHz) och hur mycket av varje resurs den använder.

Med en kombination av detta, vår syntesrapport och vår dataflödesanalys kan vi se att det tar 317338 klockcykler * 10ns klockperiod * 14 pipelinesteg = 0,04442732 sekunder. Det betyder att den totala latens som läggs till av vår bildbehandling är mindre än en tjugondelsekund (när den klockas till riktad 100MHz).

Steg 7: Lägga till IP -biblioteket i Vivado

För att använda ditt syntetiserade IP -block måste du lägga till det i Vivado.

Lägg till ett IP-arkiv i ditt projekt i Vivado genom att gå till IP-katalogen och högerklicka på "Lägg till förråd …"

Navigera till din Vivado HLS -projektkatalog och välj din lösningskatalog.

Det bör rapportera IP: n som den hittade.

Steg 8: Uppgradera

Ibland måste du göra ändringar i ditt HLS -block efter att ha inkluderat det i en Vivado -design.

För att göra detta kan du göra ändringarna och syntetisera om och exportera IP: n med ett högre versionsnummer (se detaljer i tidigare steg om större/mindre versionsnummerändringar).

Efter att du har ändrat export av den nya versionen, uppdatera dina IP -arkiv i Vivado. Detta kan antingen göras när Vivado märker att IP: n har ändrats i förvaret eller aktiverats manuellt. (Observera att om du uppdaterar dina IP -arkiv efter start, men innan exporten slutförs i HLS, kommer IP: n inte att finnas där, vänta tills den är klar och uppdateras igen.)

Vid det här laget ska ett fönster visas med informationen om att en IP har ändrats på disken och ger dig möjlighet att uppdatera den med en "Uppgradera vald" -knapp. Om ändringen var en mindre versionändring och inget av gränssnitten ändrades, Om du trycker på den knappen kommer den gamla IP -adressen automatiskt att ersättas med den nya, annars kan mer arbete behövas.

Steg 9: Ytterligare detaljer och information

Följande steg ger mer information om hur HLS -syntes fungerar och vad du kan göra med det.

För ett exempel på ett projekt som använder ett HLS -syntetiserat IP -block, se detta instruerbart.

Steg 10: Utmatning och inmatning

Utgångar och ingångar till det slutliga IP -blocket bestäms utifrån en analys som syntetiseraren gör av dataflödet in och ut ur toppfunktionen.

På samma sätt som i VHDL eller verilog kan du med HLS ange detaljer om anslutningarna mellan IP. Dessa rader är exempel på detta:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE axelport = video_in bunt = INPUT_STREAM #pragma HLS INTERFACE axelport = video_out bunt = OUTPUT_STREAM #pragma HLS INTERFACE s_axilite port = x bunt = CONTROL_BUS offset = 0x14 #pragma HLS INTERFACE = port_x1 = offs

Du kan se hur portarna som visas på IP -blocket påverkas av dessa direktiv.

Steg 11: AXI -registergränssnitt

För att få input/output till/från ditt IP -block till PS är ett bra sätt att göra detta via ett AXI -gränssnitt.

Du kan ange detta i din HLS -kod, inklusive de förskjutningar som ska användas för att komma åt värdet senare så här:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE s_axilite port = x bundle = CONTROL_BUS offset = 0x14

#pragma HLS INTERFACE s_axilite port = y bundle = CONTROL_BUS offset = 0x1C #pragma HLS dataflow

x = 42;

y = 0xDEADBEEF; }

När den väl är ansluten i Vivado kan du komma åt värdena med den här koden i Vivado SDK:

#include "parameters.h"

#define xregoff 0x14 #define yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff); y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff);

Detta kommer att få dig att sluta med 42 i x och 0xdeadbeef i y

Steg 12: Dataflow Pragma

Inuti #pragma DATAFLOW förändras sättet som koden implementeras från normal C ++. Koden är pipelined så att alla instruktioner körs hela tiden i olika delar av data (Tänk på det som ett löpande band på en fabrik, varje station arbetar kontinuerligt med att göra en funktion och överföra den till nästa station)

från bilden kan du se att var och en av direktiven

Trots att de verkar vara normala variabler implementeras faktiskt img -objekt som små buffertar mellan kommandona. Att använda en bild som ingång till en funktion "förbrukar" den och gör den inte längre användbar. (Därav behovet av dubblettkommandon)

Rekommenderad:

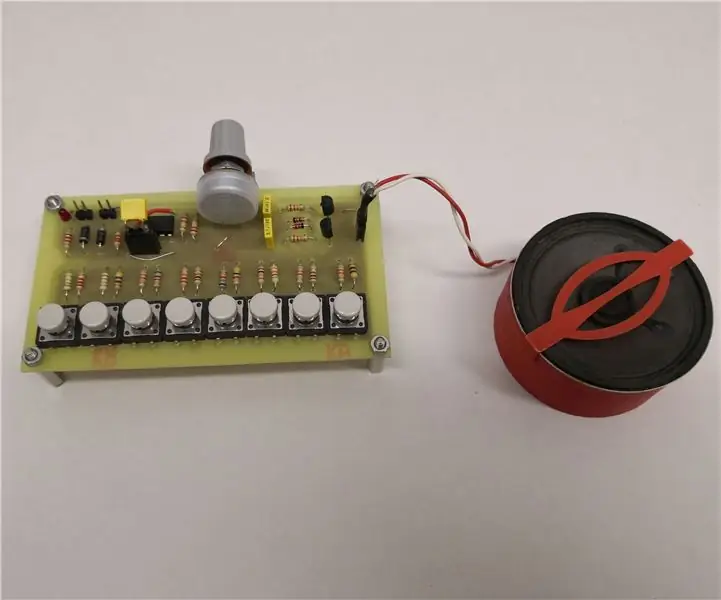

Fantastisk analog syntes/organ som endast använder diskreta komponenter: 10 steg (med bilder)

Awesome Analog Synthesizer/Organ som endast använder diskreta komponenter: Analoga synthesizers är väldigt coola, men också ganska svåra att göra.Så jag ville göra en så enkel som den kan bli, så att dess funktion kan vara lätt att förstå. För att den ska fungera kan du behöver några grundläggande delkretsar: En enkel oscillator med resis

Min första syntes: 29 steg (med bilder)

Min första synth: Kid -synthen kom till när jag satt böjd över en trasslig röra av synthesizertrådar. Min vän Oliver kom fram, utvärderade situationen och sa: "Du vet att du har lyckats göra världens mest komplicerade barnleksak." Medan mitt första r

Keytar Hero (Använda en Wii -gitarrkontroll som en syntes): 7 steg (med bilder)

Keytar Hero (Använda en Wii -gitarrkontroller som en synthesizer): Guitar Hero -spelen var raseri för ett tiotal år sedan, så det kommer säkert att finnas många gamla gitarrkontroller som ligger och samlar damm. De har många knappar, vred och spakar, så varför inte använda dem igen? Gitarrkontrollen

SENSONIZER, en DIY -syntes: 5 steg

SENSONIZER, en DIY Synthesizer: Detta är sensonizer, synthesizer baserad på sensorer.I ett nötskal Det är i grunden ett synthesizer -tangentbord, men istället för pianotangenter och vred, reglage och knappar för att styra det. Jag använde tryck- och positionssensorer för att ersätta pianotangenterna och

Oceania Midi Controller (för Make Noise 0-Coast och andra syntes): 6 steg (med bilder)

Oceania Midi Controller (för Make Noise 0-Coast and Other Synths): Under de senaste åren har ett antal synthesizer-tillverkare släppt " stationär halvmodulär " instrument. De har i allmänhet samma formfaktor som Eurorack modulära synthesizer -format och de flesta är förmodligen avsedda som en g