Innehållsförteckning:

- Författare John Day day@howwhatproduce.com.

- Public 2024-01-30 12:38.

- Senast ändrad 2025-01-23 15:10.

Av AmCoderhttps://www.linkedin.com/in/mituFölj mer av författaren:

Om: Mitu Raj - Just a Hobbyst and Learner - Chip Designer - Software Developer - Physics and Mathematics Entusiast Mer om AmCoder »

## Detta är den mest klickade, populära länken i Google för VHDL -implementering av CORDIC ALGORITHM för att generera sinus- och cosinusvåg ## För närvarande finns det många hårdvarueffektiva algoritmer, men dessa är inte välkända på grund av dominans av programvarusystem över de många åren. CORDIC är en sådan algoritm som inte är annat än en uppsättning skift- och tilläggslogiker som används för att beräkna ett brett spektrum av funktioner, inklusive vissa trigonometriska, hyperboliska, linjära och logaritmiska funktioner. Detta är algoritmen som används i miniräknare etc. Således kan vi genom att bara använda enkla shifters och adders designa en hårdvara med mindre komplexitet men kraft för DSP med hjälp av cordic algoritm. Därför kan den utformas som ren RTL -design i VHDL eller Verilog utan att använda några dedikerade flytpunktsenheter eller komplexa matematiska IP -adresser.

Steg 1: VHDL och Modelsim

Här implementeras den cordiska algoritmen med VHDL för att generera en sinusvåg och en cose -våg. Den kan mata ut sinus och cosinus för inmatningsvinkel med stor precision. Koden är syntetiserbar på FPGA. Modelsim används för att simulera designen och testbänken.

Steg 2: VHDL -kod för design och testbänk

Binär skalningsteknik används för att representera flyttal.

Gå igenom de bifogade dokumenten innan du kodar.

Gå igenomSimulera cordic_v4.vhd - Designen -Ingången är vinkel i 32 bitar + teckenbit; den kan bearbeta vilken vinkel som helst från 0 till +/- 360 grader med ingångsprecision på 0.000000000233 grader. Vid inmatning -> MSB är teckenbiten och resten 32 bitar representerar storleken. -Designens utsignal är dess sinus och cos -värde i 16 bitar + teckenbit.ie; med precision 0.00001526. Observera att utsignalen visas i 2: s komplimentsform om respektive sinus- eller cos -värde är negativt. Simulering av testb.vhd - Testbänk för konstruktionen (1) Mata in vinklar och dragåterställning = '0'. Efter två steg av simulering, återställ till "1" och "kör alla". (2) I simuleringsfönstret ställer du in radixen för sin- och cosignaler som decimal och format> Analog (automatisk). (3) Zooma ut för att se vågformen ordentligt.

Steg 3: Bifogade filer

(1) cordic_v4.vhd - Design. (2) testb.vhd - Testbänk för konstruktionen.

(3) Dokumentera hur man tvingar in vinkelinmatningar och konverterar de binära resultaten.

Uppdatering: DENNA FILER ÄR OBSELETERADE OCH GÖRES INTE MER. Vänligen använd filer från nästa steg

Steg 4: Mini -Cordic IP -kärna - 16 bitar

Begränsning av ovanstående implementering är- långsam, lägre klockfrekvens för drift på grund av beräkningar i en enda klockcykel. Mini-Cordic IP Core- 16 Bit

- Kritiska vägar fördelade på flera cykler för att förbättra prestanda.- Snabbare- FPGA beprövad design syntetiseras upp till 100 Mhz klocka.- Mer yta optimerat i HDL, Mindre hårdvara.- Belastnings- och klara statussignaler tillagda.- Endast nackdelen är lägre upplösning jämfört med föregående. Testbänk:

helt automatiserad från 0 till 360 graders vinkelingångar

Bifogade filer: 1) mini cordic main vhdl file2) mini cordic test bench3) Mini Cordic IP Core manual4) Doc om hur man tvingar vinklar och konverterar resultat

För frågor, kontakta mig gärna:

Mitu Raj

följ mig:

mail: iammituraj@gmail.com

### Totalt antal nedladdningar: 325 från och med 01-05-2021 ###

### Koden redigerades senast: 07-07-2020 ###

Rekommenderad:

Self Balancing Robot - PID Control Algoritm: 3 steg

Self Balancing Robot - PID Control Algorithm: Detta projekt var tänkt för att jag var intresserad av att lära mig mer om kontrollalgoritmer och hur man effektivt implementerar funktionella PID -loopar. Projektet är fortfarande i utvecklingsfas eftersom en Bluetooth -modul ännu inte ska läggas till som kommer

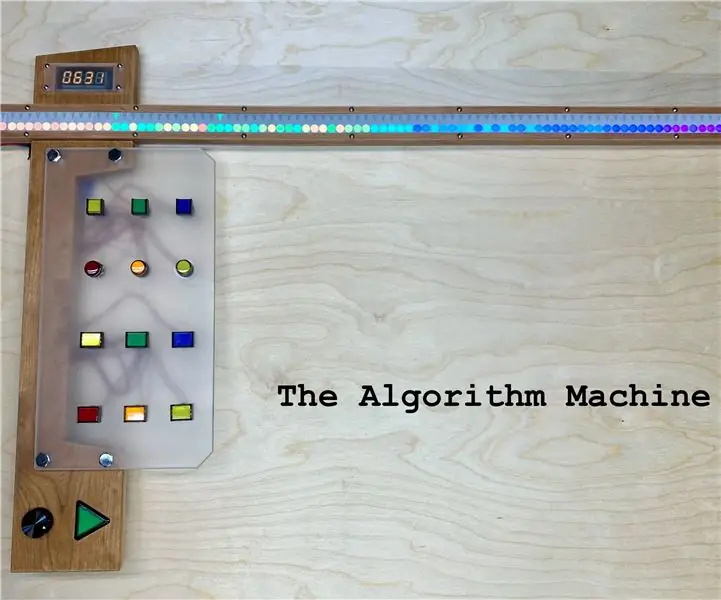

Algoritm maskinen: 13 steg (med bilder)

Algoritmmaskinen: Jag har undervisat i datavetenskap på högskolenivå i 15 år, och även om min expertis är mer på programmeringssidan, spenderar jag fortfarande ganska mycket tid på att täcka standardalgoritmer för sökning och sortering. Ur undervisningssynpunkt

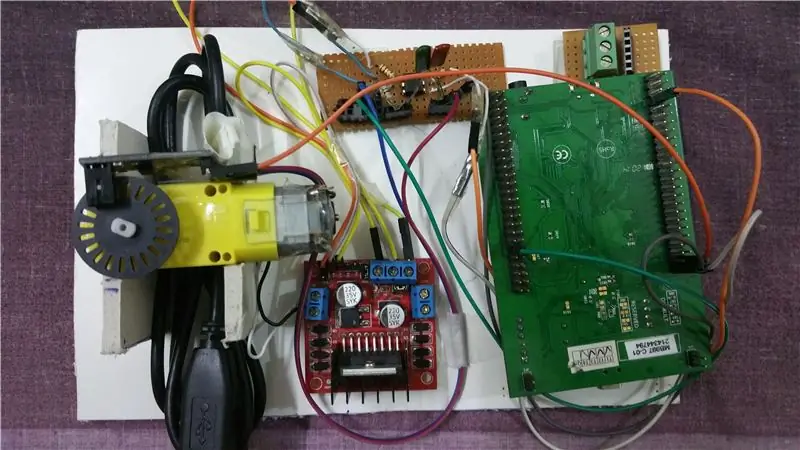

Självbalanseringsrobot med PID -algoritm (STM MC): 9 steg

Självbalanseringsrobot med hjälp av PID -algoritm (STM MC): Nyligen har mycket arbete gjorts i självbalansering av objekt. Begreppet självbalansering började med balansering av inverterad pendel. Detta koncept utvidgades även till design av flygplan. I detta projekt har vi designat en liten mod

Tic Tac Toe på Arduino med AI (Minimax -algoritm): 3 steg

Tic Tac Toe på Arduino med AI (Minimax Algoritm): I denna instruktionsbok ska jag visa dig hur du bygger ett Tic Tac Toe -spel med en AI med hjälp av en Arduino. Du kan antingen spela mot Arduino eller titta på Arduino spela mot sig själv. Jag använder en algoritm som kallas " minimax algoritm ",

Hastighetsreglering av likströmsmotor med PID -algoritm (STM32F4): 8 steg (med bilder)

Hastighetsreglering av likströmsmotor med PID -algoritm (STM32F4): hej alla, det här är ett annat projekt. Den här gången är det STM32F407 som MC. Detta är ett projekt i mitten av terminen. Hoppas du gillar det. Det kräver många koncept och teori så vi går in på det först. Med tillkomsten av datorer och