Innehållsförteckning:

- Steg 1: Skapa en PWM-modul- källfil

- Steg 2: Bygga en PWM-modul- Vivado Setup

- Steg 3: Bygga en PWM-modul- Skapa en projektfil

- Steg 4: Bygga en PWM-modul- Blockdesign och begränsningsfilinställning (I)

- Steg 5: Bygga en PWM-modul- Blockdesign och begränsningsfilinställning (II)

- Steg 6: Bygga en PWM-modul- Blockdesign och begränsningsfilinställning (III)

- Steg 7: Bygga en PWM-modul- Blockdesign och begränsningsfilinställning (IV)

- Steg 8: Bygga en PWM-modul- Blockdesign och begränsningsfilinställning (V)

- Steg 9: Bygga en PWM-modul- Hårdvaruinstallation

- Steg 10: Bygga en PWM-modul- Generera Bitstream och starta SDK

- Steg 11: Bygga en PWM-modul- Skapa en ny applikation i Xilinx SDK

- Steg 12: Bygga en PWM-modul- Översikt över Project Explorer (I)

- Steg 13: Bygga en PWM-modul- Översikt över Project Explorer (II)

- Steg 14: Bygga en PWM-modul- Översikt över Project Explorer (III)

- Steg 15: Bygga en PWM-modul- Avsluta PWM-funktionen (I)

- Steg 16: Bygga en PWM-modul- Avsluta PWM-funktionen (II)

- Steg 17: Bygga en PWM-modul- Avsluta PWM-funktionen (III)

- Steg 18: Bygga en PWM-modul- Få det att köra

- Steg 19: Streaming av videobearbetning på Digilent ZYBO med OV7670

- Steg 20: Komplett blockdiagram

- Steg 21: Anslut OV7670 till ZYBO

- Steg 22: Skapa blockdesign

- Steg 23: Lägg till VHDL -filer för OV7670 kamerakontroll och inspelning

- Steg 24: Lägg till begränsningsfil

- Steg 25: Lägg till IP Repo för HLS IP

- Steg 26: Lägg till moduler och IP

- Steg 27: IP -konfigurationsinställningar

- Steg 28: Lägg till och konfigurera PS IP Block

- Steg 29: Del 1. Bygga en PWM -modul för servomotorer

- Steg 30: Sidanslutningar för videoingång (aclk markerad)

- Steg 31: Anslutningar till OV7670

- Steg 32: Anslutningar på Video Out Side

- Steg 33: Kör Block and Connection Automation

- Steg 34: Generera HDL Wrapper

- Steg 35: Generera Bitstream, exportera hårdvara till SDK, starta SDK från Vivado

- Steg 36: SDK (inga FreeRTOS)

- Steg 37: FreeRTOS -implementering

- Steg 38: Användningsinstruktioner

- Steg 39: Referenser och länkar

- Författare John Day day@howwhatproduce.com.

- Public 2024-01-30 12:46.

- Senast ändrad 2025-01-23 15:11.

Börja med steg ett för detaljer om hur du bara skapar en 2-axlig servo PWM-styrenhet.

Börja med det massiva blockdiagrammet (steg 19) för hela projektet.

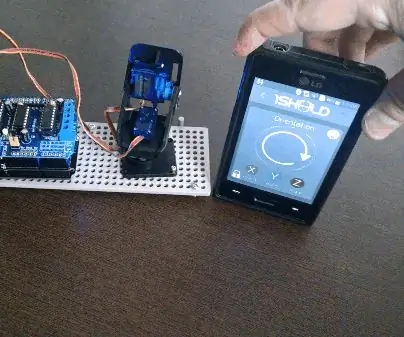

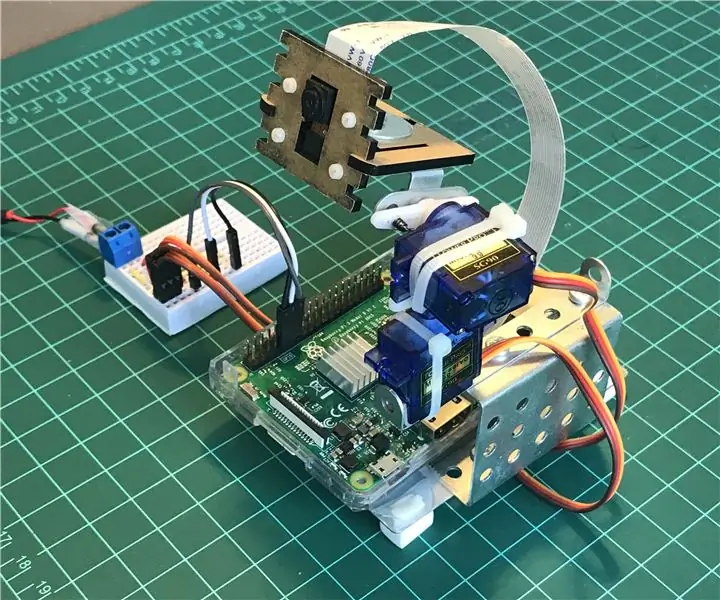

Kamera + Pan/tilt -inställning som vi använde:

PmodCON3 från Digilent användes för att ansluta servon.

Steg 1: Skapa en PWM-modul- källfil

Steg 2: Bygga en PWM-modul- Vivado Setup

Ladda först ner Vivado Design Suite From Xilinx webbplats. Installera hela designpaketet, inklusive Vivado Software Development Kit (SDK). Detta projekt använder versionen 2017.2.

Under tiden bör Digilent Adept 2 också installeras som en Zybo -kortdrivrutin.

Steg 3: Bygga en PWM-modul- Skapa en projektfil

Innan du skapar en projektfil bör du se till att du redan har installerat Zybo -filen ordentligt som självstudien här:

Vivado version 2015.1 och senare kortfilinstallation

Öppna Vivado 2017.2. Vid snabbstart klickar du på Skapa projekt -> Nästa -> Projektnamn (Ge ditt projektnamn här) -> Projekttyp. Välj Projekttyp, välj RTL -projekt och markera "Ange inte källor just nu". Välj sedan "Brädor" och "Zybo" som visningsnamn för standarddelen. Klicka sedan på Slutför för att starta projektet.

Steg 4: Bygga en PWM-modul- Blockdesign och begränsningsfilinställning (I)

Klicka på “” Skapa blockdesign”i Flow Navigator och tryck sedan på OK. klicka på "+" -tecknet för att lägga till nödvändiga IP -adresser. Lägg till:

- Ett ZYNQ7 -bearbetningssystem Två AXI -timer

- Två AXI -timer

Steg 5: Bygga en PWM-modul- Blockdesign och begränsningsfilinställning (II)

Efter att du har lagt till IP -adresser, kör blockautomatisering och anslutningsautomation. När automatiseringen är klar högerklickar du på blocket”axi_timer_0” på pwm0 -> Make External. Namnge pwm0 extern stift som pwm_Xaxis. Upprepa också ovanstående process på blocket "axi_timer_1" och namnge pwm0 extern stift som pwm_Zaxis.

Steg 6: Bygga en PWM-modul- Blockdesign och begränsningsfilinställning (III)

Lägg märke till att varje gång vi avslutar Blockdesignen i Vivado måste vi skapa en HDL Wrapper. Eftersom det kommer att vara modulen på högsta nivå för varje projekt.

Steg 7: Bygga en PWM-modul- Blockdesign och begränsningsfilinställning (IV)

Nu måste vi konfigurera vår begränsningsfil för att tilldela stift som är anslutna till vårt blockschema. Stäng fönstret Blockdesign, på fliken Källor, "Lägg till källor"-> Lägg till eller skapa begränsningar-> lägg till Zybo-Master.xdc som våra begränsningsfiler.

Steg 8: Bygga en PWM-modul- Blockdesign och begränsningsfilinställning (V)

Öppna begränsningsfilen Zybo-Master.xdc från mappen Begränsningar, avmarkera portarna som vi vill ange som utsignaler och byt namn på "get_ports {XXXX}", som XXXX betecknar den externa stift som heter i blockdiagrammet. Inställningen av begränsningsfil visas i figuren.

Steg 9: Bygga en PWM-modul- Hårdvaruinstallation

Anslut servomotorerna till Pmod CON3. TowerPro SG90 är servomotormodellen vi använde i detta projekt. För servomotortråden representerar den orangea ledningen PWM -signalen, ansluten till SIG -stiftet i Pmod CON3. Den röda ledningen Vcc är en strömkabel ansluten till VS -stift i Pmod CON3. Slutligen är den bruna tråden Gnd en jordledning ansluten till GND -stiftet. Sätt sedan in Pmod CON3 på den övre raden av JD -porten i Zybo -kortet.

Steg 10: Bygga en PWM-modul- Generera Bitstream och starta SDK

1. på fliken Project Navigator, kör Generera BitStream.

2. Exportera hårdvara: Arkiv> Exportera> Exportera hårdvara-> markera på "inkludera bitström"-> OK 3. Lansera SDK: Arkiv-> Starta SDK.

Steg 11: Bygga en PWM-modul- Skapa en ny applikation i Xilinx SDK

Skapa en ny applikation:

Arkiv> Ny> Applikationsprojekt -> Ange projektets namn -> Slutför

Under Project Explorer ska det finnas tre mappar.

I det här fallet är “design_1_wrapper_hw_platform_0” den mapp som tidigare exporterats av Vivado. Axis_2_PWM_SDK_bsp är mappens supportpaket. Och Axis_2_PWM_SDK är vår huvudprojektmapp i SDK. Du kan se filen "helloworld.c" under mappen "src" i Axis_2_PWM_SDK, där "helloworld.c" är huvudfilen.

Steg 12: Bygga en PWM-modul- Översikt över Project Explorer (I)

Låt oss kontrollera några filer under Project Explorer. Först öppnar du "system.hdf" i mappen "design_1_wrapper_hw_platform_0". Denna fil visar adresskartan för processor ps7_cortex9 och IP -blocken som finns i vår design.

Steg 13: Bygga en PWM-modul- Översikt över Project Explorer (II)

Kontrollera sedan filen "inkludera" och "libsrc" under mappen "Axis_2_PWM_SDK_bsp". Biblioteksfiler här gör att vi kan interagera med hårdvaruutrustning utan att “spela” register.

Steg 14: Bygga en PWM-modul- Översikt över Project Explorer (III)

Genom BSP -dokumentationen finns xtmrctr.h som ett Xilinx Timer Control Library relaterat till AXI Timer. Vanligtvis kan vi hitta önskad PWM -funktion här. Men om du läser dokumentationen "tmrctr_v4_3", visar det att drivrutinen för närvarande inte stöder PWM -driften av enheten. På grund av bristen på PWM -funktion måste vi avsluta vår PWM -funktion med hjälp av xtmrctr.h och AXI Timer v2.0 LogiCORE IP Product Guide.

Steg 15: Bygga en PWM-modul- Avsluta PWM-funktionen (I)

Tillbaka till huvudfilen “helloworld.c”, inkludera följande rubrikfiler:

Steg 16: Bygga en PWM-modul- Avsluta PWM-funktionen (II)

Definiera basadresserna för två AXI TImer genom “xparameters.h”.

Steg 17: Bygga en PWM-modul- Avsluta PWM-funktionen (III)

Skapa önskad PWM -funktion.

Duty_val: konverterar gradvärdet till duty cycle. PWM_Freq_Duty: ställ in önskad frekvens och driftcykel för att generera PWM. Klockperiod bör också tilldelas.

PWM_START: tilldela PWM -registeradressen och börja generera PWM.

PWM_STOP: tilldela PWM -registeradressen och sluta generera PWM.

Resten av demokoden visas i "helloworld.c" under "Axis_2_PWM_SDK"

Steg 18: Bygga en PWM-modul- Få det att köra

1. Programmera FPGA genom SDK

- Anslut Zybo -kortet via USB -porten till datorn.

- Xilinx Tools -> Program FPGA

2. Kör programmet

Klicka på "Kör" -ikonen och släpp ner menyn -> Kör som -> Starta på maskinvara

3. SDK -terminal

- Öppna SDK -terminalen -> Anslut till seriell port -> OK

- Kör programmet. Om demokoden körs framgångsrikt bör du se "Initialisering klar!" på SDK -terminalen.

Steg 19: Streaming av videobearbetning på Digilent ZYBO med OV7670

Komplett arkivfil bifogad.

Steg 20: Komplett blockdiagram

Detta visar hela diagrammet över alla anslutningar och IP -block i projektet

Steg 21: Anslut OV7670 till ZYBO

Skapa en anslutning för att ansluta ov7670 -modulen till ZYBO Pmods

Data Pmod är Pmod D

Kontroll Pmod är Pmod C

Anslut dessutom PmodCON3 och servon enligt specifikationen i den första halvan av denna handledning

Steg 22: Skapa blockdesign

Klicka på "Skapa blockdesign" i Flow Navigator och tryck sedan på OK.

Steg 23: Lägg till VHDL -filer för OV7670 kamerakontroll och inspelning

Lägg till de VHDL -filer som bifogas detta steg till projektet

Steg 24: Lägg till begränsningsfil

Lägg till den bifogade begränsningsfilen till ditt projekt.

Steg 25: Lägg till IP Repo för HLS IP

Ta den bifogade zip -filen och packa upp den i en ny mapp med samma namn i en ny katalog (mapp) som heter "HLS_repo".

Lägg till ett IP-arkiv i ditt projekt genom att gå till IP-katalogen och högerklicka på "Lägg till lagringsplats …"

Navigera till din "HLS_repo" -katalog och välj den.

Valfritt: Skapa HLS -videobearbetningsblocket själv!

Steg 26: Lägg till moduler och IP

Lägg till modulerna ov7670_axi_stream_capture, debounce och ov7670_controller i blockdiagrammet genom att högerklicka på bakgrunden och välja "Lägg till modul …"

Lägg på samma sätt till IP: erna:

- HLS_Video_Track

- Videorambuffert Skriv

- Videorambuffert läst

- Video Timing controller

- AXI4-Stream till Video Out

- 3 av "Slice"

- Konstant

- 2 av AXI -timer

Steg 27: IP -konfigurationsinställningar

Som visas på bilderna

Steg 28: Lägg till och konfigurera PS IP Block

Lägg till ZYNQ7 Processing System i blockschemat

redigera konfigurationen:

-

PS-PL-konfiguration

-

HP

- Aktivera S HP 0

- Aktivera S HP 1

-

-

Klocka konfiguration

-

PL Tygklockor

- FCLK_0 vid 100MHz

- FCLK_1 vid 25MHz (OutputClock)

- FLCK_2 vid 35MHz (<= 50MHz) (CameraClock)

-

Steg 29: Del 1. Bygga en PWM -modul för servomotorer

Ta fram axi_timer_0 pwm0 till den nya utgångsporten pwm_Xaxis

Ta fram axi_timer_1 pwm0 till den nya utgångsporten pwm_Zaxis

Steg 30: Sidanslutningar för videoingång (aclk markerad)

Anslut videoingångens IP -block korrekt

(* dessa anslutningar bör skapas genom att välja rätt alternativ under anslutningsautomatisering) "aclk" från axi_stream_capture går till:

- ap_clk på videorambuffertskrivning

- ap_clk på HLS -videoströmbehandlingsblock

- *aclk på AXI smartconnect IP från Video Frame Buffer Skriv till S_AXI_HP0

- *aclk motsvarande kanalerna för AXI Interconnect IP för S_AXI -kanalerna i HLS -videobearbetningsblocket och videorambufferten skriva S_AXI_HP0_ACLK på PS -blocket

Videoströmssignalen kopplas helt enkelt i serie från inspelningsblocket till Zynq -minnesgränssnittet.

- Video går från inspelningsblock till HLS -bearbetningsblock.

- Den bearbetade videon från HLS -blocket går till rambuffertens skrivblock.

- *Rambuffertens skrivblock ansluter till HP0 -gränssnittet på Zynq PS -blocket.

- M_axis_tuser -signalen från utsignalen från registreringsblocket kopplas manuellt till både video_in_TUSER -insignalen på HLS -behandlingsblocket och ap_start -signalen på samma block.

TUSER (tuser) -signalen används av AXI -videoströmprotokollet för att indikera starten på en bildruta i videon. AP_Start säger till HLS -blocket att börja bearbeta. Vi använder alltså tuser för att trigga HLS -blocket för att bearbeta varje bildruta som det kommer in. När du ansluter en enda signal från en buss och delar upp den på detta sätt är det nödvändigt att också ansluta den till den normala avslutningspunkten för resten av bussen. Vivado antar att om du ansluter signalen manuellt så vill du koppla bort vad den normalt skulle ansluta till.

Konfigurationsinställningar för IP -block:

Videoram buffert skriv:

Videoformat: RGB8

1 prov per klocka Max kolumner: 1280 (> = 640) Max rader: 960 (> = 480) Max data bredd: 8

Steg 31: Anslutningar till OV7670

På blocket ov7670_axi_stream_capture

- Gör alla ingångar externa (högerklicka på en nål och välj från menyn, eller vänsterklicka-> ctrl+T)

- Lämna namnen som de är

På blocket ov7670_controller

- Gör alla blockutgångar externa

- Byt namn på config_finished -porten till led0

- anslut clk till CameraClock (<= 50MHz) (FCLK_2)

På debounce -blocket

- anslut knapp 1 -ingången till en extern ingångsport som kallas btn0

- anslut out1 till skicka igen på ov7670_controller IP -block

- anslut knapp 2 -ingången till en extern ingångsport som kallas btn3

- anslut out2n till ext_reset_in -ingången på processorsystemets återställnings -IP för klockdomänen för videoinspelning. (*Detta kan behöva göras efter att IP har genererats*)

- anslut clk till CameraClock (<= 50MHz) (FCLK_2)

Steg 32: Anslutningar på Video Out Side

Anslutningar för block Video Timing Controller (VTC), AXI4-Stream till Video Out och skivor

- Använd 25MHz klocka (FCLK_1) för vid_io_out_clk och VTC clk

- Använd 100MHz klocka (FCLK_0) för aclk på AXI4-Stream to Video Out

- vtiming_out till vtiming_in

- Video Frame Buffer Läs m_axis_video går till AXI4-Stream till Video Out video_in

- vtg_ce går till gen_clken

- Knyt VTC clken, aclken, vid_io_out_ce till Constant dout [0: 0]

- Ta med vid_hsync och vid_vsync till externa utgångsportar vga_hs respektive vga_vs. (inte på bilden)

Skivor:

-

Skivor bör installeras som visas i bifogade bilder

- döpa om blocken till slice_red, slice_green och slice_blue

- setup -segmentintervall som visas på bilderna per blockets namn

- anslut varje segmentutmatning till en extern portutgång enligt bilden.

- vid_data [23: 0] ansluter till ingångarna för varje segment (Din [23: 0])

Steg 33: Kör Block and Connection Automation

Kör Block Automation för att ansluta sakerna från ZYNQ7 PS -blocket. Som visas på bilden.

Kör anslutningsautomatisering för att skapa all sammankopplings -IP. Var noga med alla alternativ i varje bild.

På debounce -blocket ansluter du out2n till videoinspelningsklockans domän Processor System Reset ext_reset_in input.

Steg 34: Generera HDL Wrapper

Generera HDL Wrapper för din blockdesign.

Ställ in den som den översta modulen.

Steg 35: Generera Bitstream, exportera hårdvara till SDK, starta SDK från Vivado

Se till att inkludera bitström i exporten.

Generering av bitström kan ta mycket lång tid.

Starta sedan SDK

Steg 36: SDK (inga FreeRTOS)

Denna version gör allt utan att använda FreeRTOS, vilket kondenserar koden snyggt.

Skapa en fristående BSP baserad på hårdvarudesign. Standardalternativen ska vara bra. Se till att BSP -källor har genererats.

Skapa app enligt bilden. (tom ansökan)

Ta bort det autogenererade huvudet och importera de bifogade filerna.

Steg 37: FreeRTOS -implementering

Denna version använder FreeRTOS. Create a FreeRTOS901 BSP based on the hardware design. Standardalternativen ska vara bra. Se till att BSP -källor har genererats.

Skapa app enligt bilden. (tom ansökan)

Ta bort det autogenererade huvudet och importera de bifogade filerna.

Steg 38: Användningsinstruktioner

Det här projektet är lite knepigt att komma igång. Följ stegen i ordning.

Se till att din ZYBO inte laddar något själv när den slås på. Det betyder att Done -lampan inte ska tändas. Ett sätt att göra detta är att ställa in startkällbygeln till JTAG.

Öppna projektet (FreeRTOS eller inte) som du vill programmera från SDK

- Slå på din ZYBO. Done -lampan ska inte lysa.

- Programmera FPGA med bitfilen. Done -lampan ska lysa. Led0 ska inte lysa.

- Kör koden (kom ihåg att gå förbi startbrytpunkten om du gör det).

Vid denna tidpunkt bör du få en utgång på din VGA -skärm.

För att starta om (om det är fel eller vad som helst): tryck snabbt på PS-SRST-knappen eller stäng av ZYBO och slå sedan på den igen. Fortsätt från steg 2.

Om du stannar processorn med felsökaren kommer kameran att hålla position istället för att flytta. Videoströmmen fortsätter ändå.

Steg 39: Referenser och länkar

Xilinx referensguider och dokumentation:

- PG044 - AXI -Stream to Video Out

- PG278 - Videorambuffert Läs/skriv

Andra länkar:

- Lauris blogg - VDMA -ingång

- Lauris blogg - OV7670 till VGA -utgång med BRAM

- Hamsterworks wiki, av Mike Fields, den ursprungliga källan till OV7670 -koden

- Datablad med grundläggande tidsspecifikationer

Rekommenderad:

Pan Tilt kontrolleras av mobiltelefon: 4 steg

Pan Tilt kontrollerad av mobiltelefon: Hej alla, I detta nya projekt kommer jag att presentera en Pan-Tilt som styrs av mobiltelefon.Alla rörelser i mobiltelefonen återges i pan-tilt-enheten via Bluetooth.Konstruktionen är mycket enkelt med en Arduino R3 (eller liknande) och två

Pan- och tilt -mekanism för DSLR -tidsförlopp: 7 steg (med bilder)

Pan and Tilt Mechanism for DSLR Time Lapses: Jag hade några stegmotorer liggande och ville verkligen använda dem för att göra något coolt. Jag bestämde mig för att jag skulle göra ett Pan and Tilt -system för min DSLR -kamera så att jag kan skapa coola tidsförlopp. Artiklar du behöver: 2x stegmotorer -htt

IOT123 - SOLAR TRACKER - TILT/PAN, PANEL RAM, LDR MOUNTS RIG: 9 Steg (med bilder)

IOT123 - SOLAR TRACKER - TILT/PAN, PANEL RAM, LDR MOUNTS RIG: De flesta DIY -konstruktionerna för tvåaxliga solspårare " där ute " är baserade på 9G Micro Servo som verkligen är undervärderade för att driva runt ett par solceller, mikrokontrollen, batteriet och höljet. Du kan designa runt

Pan-Tilt Multi Servo Control: 11 steg (med bilder)

Pan-Tilt Multi Servo Control: I den här självstudien kommer vi att utforska hur du styr flera servon med Python på en Raspberry Pi. Vårt mål kommer att vara en PAN/TILT -mekanism för att placera en kamera (en PiCam) .Här kan du se hur vårt slutliga projekt kommer att fungera: Control Servo Control loop test:

Fjärrstyrd pan och tilt -head: 7 steg

Fjärrstyrd pan och tilt head: Jag ville alltid ha en fjärrstyrd pan och tilt head. Kanske var det för min videokamera, en gummibandsskytt eller en vattenpistol riktare. Det spelar egentligen ingen roll vad du lägger på övre däck (så länge det inte är för tungt), med det här lilla projektet