Innehållsförteckning:

- Författare John Day day@howwhatproduce.com.

- Public 2024-01-30 12:44.

- Senast ändrad 2025-01-23 15:11.

Jag kommer att analysera hur DC-DC-teknikens utmaning för strömförsörjningsdesign möts.

Kraftsystemkonstruktörer står inför konstant press från marknaden för att hitta sätt att få ut det mesta av tillgänglig ström. I bärbara enheter förlänger högre effektivitet batteriets livslängd och lägger mer funktionalitet i mindre paket. I servrar och basstationer kan effektivitetsvinster direkt spara infrastruktur (kylsystem) och driftskostnader (elräkningar). För att möta marknadens krav förbättrar systemdesigners effektomvandlingsprocesser inom flera områden, inklusive effektivare kopplingstopologier, paketinnovationer och nya halvledaranordningar baserade på kiselkarbid (SiC) och galliumnitrid (GaN).

Steg 1: Förbättring av Switching Converter Topology

För att dra full nytta av tillgänglig kraft, antar människor alltmer design baserade på switchningsteknik snarare än linjär teknik. Växelströmförsörjningen (SMPS) har en effektiv effekt på över 90%. Detta förlänger batteriets livslängd för bärbara system, minskar kostnaden för el för stor utrustning och sparar utrymme som tidigare använts för kylflänskomponenter.

Att byta till en växlad topologi har vissa nackdelar, och dess mer komplexa design kräver att designers har flera färdigheter. Designingenjörer måste vara bekanta med analog och digital teknik, elektromagnetik och sluten slinga. Utformare av kretskort (PCB) måste ägna mer uppmärksamhet åt elektromagnetisk interferens (EMI) eftersom högfrekventa kopplingsvågformer kan orsaka problem i känsliga analoga och RF -kretsar.

Innan transistorn uppfanns, föreslogs det grundläggande konceptet med omkoppling av strömomvandling: till exempel induktivt urladdningssystem av Kate-typ som uppfanns 1910, som använde en mekanisk vibrator för att implementera en flyback-boost-omvandlare för ett tändsystem för bilar.

De flesta standardtopologier har funnits i årtionden, men det betyder inte att ingenjörer inte justerar standarddesign för att ta emot nya applikationer, särskilt kontrollslingor. Standardarkitekturen använder en fast frekvens för att bibehålla en konstant utspänning genom att mata tillbaka en del av utspänningen (spänningslägesstyrning) eller styra den inducerade strömmen (strömlägesstyrning) under olika belastningsförhållanden. Designers förbättras ständigt för att övervinna bristerna i den grundläggande designen.

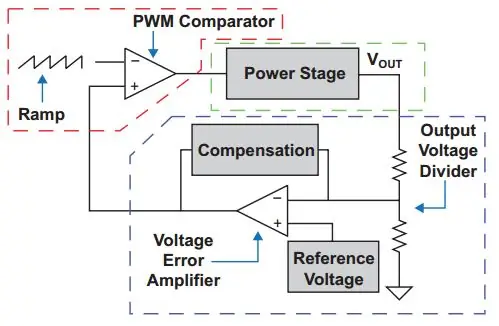

Figur 1 är ett blockschema över ett grundläggande system för sluten spänningsläge (VMC). Effektsteget består av en strömbrytare och ett utgångsfilter. Kompensationsblocket innefattar en utspänningsdelare, en felförstärkare, en referensspänning och en slingkompensationskomponent. En pulsbreddsmodulator (PWM) använder en komparator för att jämföra felsignalen med en fast rampsignal för att producera en utgångspulssekvens som är proportionell mot felsignalen.

Även om de olika belastningarna i VMC -systemet har strikta utgångsregler och är lätta att synkronisera med den externa klockan, har standardarkitekturen vissa nackdelar. Slingkompensation minskar styrbreddens bandbredd och saktar ner det övergående svaret; felförstärkaren ökar driftströmmen och minskar effektiviteten.

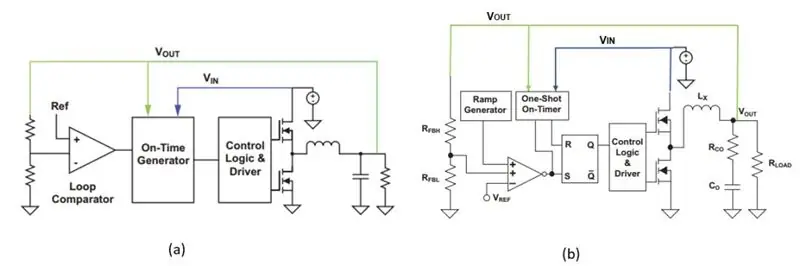

Det konstanta kontrollsystemet (COT) ger god övergående prestanda utan slingkompensation. COT-kontrollen använder en komparator för att jämföra den reglerade utspänningen med referensspänningen: när utspänningen är mindre än referensspänningen genereras en fast tidspuls. Vid låga driftcykler orsakar detta att omkopplingsfrekvensen är mycket hög, så den adaptiva COT-regulatorn genererar en tid som varierar med in- och utspänningarna, vilket håller frekvensen nästan konstant vid steady state. Texas Instruments D-CAP-topologi är en förbättring jämfört med den adaptiva COT-metoden: D-CAP-regulatorn lägger till en rampspänning till feedbackkomparatorens ingång, vilket förbättrar jitterprestanda genom att minska brusbandet i applikationen. Figur 2 är en jämförelse av COT- och D-CAP-systemen.

Figur 2: Jämförelse av standard COT-topologi (a) och D-CAP-topologi (b) (Källa: Texas Instruments) Det finns flera olika varianter av D-CAP-topologin för olika behov. Till exempel använder TPS53632 halvbrygga PWM-styrenheten D-CAP+ -arkitekturen, som främst används i applikationer med hög ström och kan driva effektnivåer upp till 1MHz i 48V till 1V POL-omvandlare med effektivitet så hög som 92%.

Till skillnad från D-CAP lägger D-CAP+ feedback loop till en komponent som är proportionell mot den inducerade strömmen för exakt droopkontroll. Den ökade felförstärkaren förbättrar DC -lastens noggrannhet under en rad olika linje- och belastningsförhållanden.

Styrenhetens utspänning ställs in av den interna DAC. Denna cykel börjar när den aktuella återkopplingen når felspänningsnivån. Denna felspänning motsvarar den förstärkta spänningsskillnaden mellan DAC -börvärdesspänningen och återkopplingsutgångsspänningen.

Steg 2: Förbättra prestanda under låga belastningsförhållanden

För bärbara och bärbara enheter finns det ett behov av att förbättra prestandan under låga belastningsförhållanden för att förlänga batteriets livslängd. Många bärbara och bärbara applikationer är för det mesta i ett "tillfälligt viloläge" eller "viloläge" i vänteläge för det mesta, bara aktiverat som svar på användarinmatning eller periodiska mätningar, så minimera strömförbrukningen i vänteläge. Det är högsta prioritet.

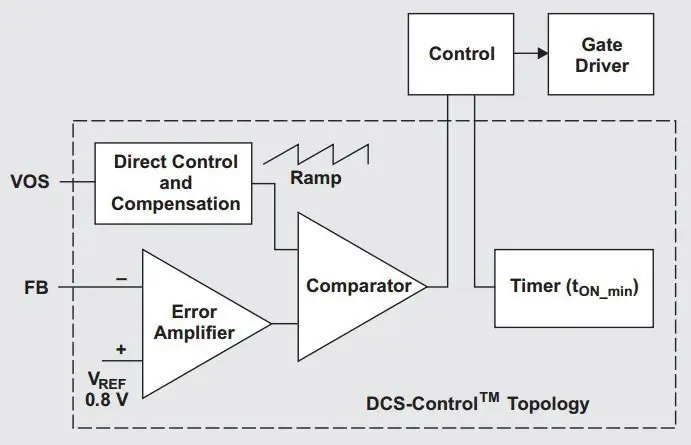

DCS-ControlTM (Direct Control to Seamless Transition to Energy Saver Mode) topologi kombinerar fördelarna med tre olika kontrollscheman (dvs hysteresläge, spänningsläge och strömläge) för att förbättra prestanda under ljusbelastningsförhållanden, särskilt övergång till Eller när lämnar lätt belastning. Denna topologi stöder PWM -lägen för medelstora och tunga laster, samt energisparläge (PSM) för lätta laster.

Under PWM -drift fungerar systemet med sin nominella kopplingsfrekvens baserat på ingångsspänningen och styr frekvensändringen. Om belastningsströmmen minskar växlar omvandlaren till PSM för att bibehålla hög effektivitet tills den sjunker till en mycket lätt belastning. Vid PSM minskar omkopplingsfrekvensen linjärt med belastningsström. Båda lägena styrs av ett enda kontrollblock, så övergången från PWM till PSM är sömlös och påverkar inte utspänningen.

Figur 3 är ett blockschema över DCS-ControlTM. Styrslingan tar information om förändringen i utspänningen och matar den direkt tillbaka till den snabba komparatorn. Komparatorn ställer in omkopplingsfrekvensen (som en konstant för driftstillstånd i stationära tillstånd) och ger en omedelbar reaktion på dynamiska belastningsförändringar. Spänningsåterkopplingsslingan reglerar DC -belastningen exakt. Det internt kompenserade regleringsnätet möjliggör snabb och stabil drift med små externa komponenter och låga ESR -kondensatorer.

Figur 3: Implementering av DCS-ControlTM-topologin i TPS62130-buckomvandlaren (Källa: Texas Instruments)

TPS6213xA-Q1 synkron växelströmskonverterare är baserad på DCS-ControlTM-topologin och är optimerad för POL-applikationer med hög effektdensitet. Den typiska 2,5 MHz omkopplingsfrekvensen tillåter användning av små induktorer och ger snabb övergående respons och hög utgångsspänningsnoggrannhet. TPS6213 arbetar från ett ingångsspänningsområde från 3V till 17V och kan leverera upp till 3A kontinuerlig ström mellan 0,9V och 6V utspänningar.

Rekommenderad:

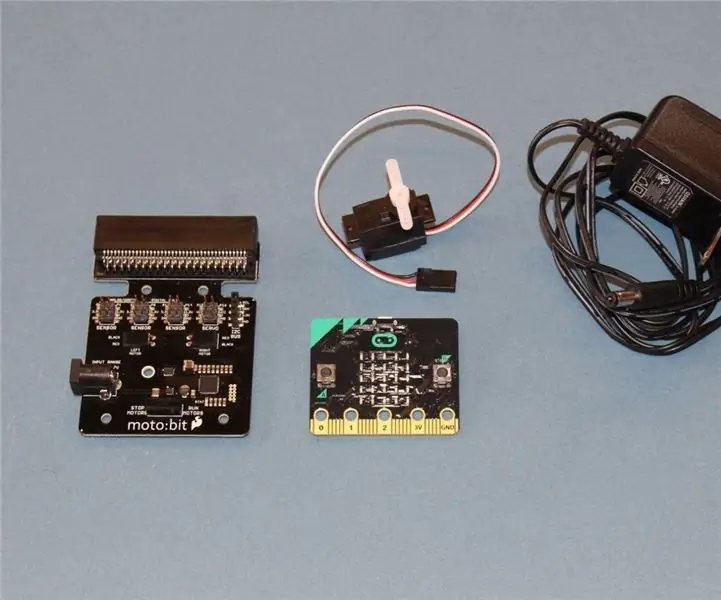

Hur man kör servomotorer med Moto: bit med mikro: bit: 7 steg (med bilder)

Så här kör du servomotorer med Moto: bit med Micro: bit: Ett sätt att utöka funktionaliteten för micro: bit är att använda ett kort som heter moto: bit av SparkFun Electronics (cirka $ 15-20). Det ser komplicerat ut och har många funktioner, men det är inte svårt att köra servomotorer från det. Moto: bit låter dig

Hur man avlägsnar polariteten hos vanliga elektronikkomponenter: 7 steg

Hur man kan dra av polariteten hos vanliga elektronikkomponenter: Försök någonsin att återanvända en lysdiod, för att inte veta vilken sida som är positiv eller negativ? Rädsla inte mer! I den här instruktionsboken kommer jag att ge dig tips om hur du hittar polariteten hos vanliga elektronikkomponenter

Rotary Encoder: Hur det fungerar och hur det används med Arduino: 7 steg

Rotary Encoder: Hur det fungerar och hur det används med Arduino: Du kan läsa detta och andra fantastiska självstudier på ElectroPeaks officiella webbplats Översikt I den här självstudien får du veta hur du använder roterande kodare. Först ser du lite information om rotationsgivaren, och sedan lär du dig hur

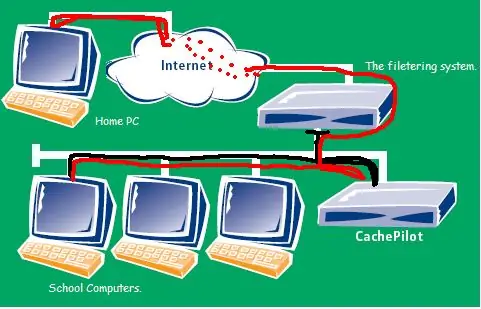

Bypassfiltreringssystem på datorer utan osäkerheten hos TOR (lökroutern) eller Tunneling Internet Over SSH: 5 steg

Bypass -filtreringssystem på datorer utan osäkerheten hos TOR (Onion Router) eller Tunneling Internet Over SSH: Efter att ha läst ett inlägg om lökroutern (tor) som låter dig kringgå censur utan att spåras blev jag förvånad. Sedan läste jag att det inte var särskilt säkert eftersom vissa noder kunde mata in falska data och ta tillbaka fel sidor. Tänkte jag själv

Hur man gör en morföräldrars kalender & Klippbok (även om du inte vet hur du ska klippbok): 8 steg (med bilder)

Hur man gör en morföräldrars kalender & Klippbok (även om du inte vet hur du ska klippbok): Detta är en mycket ekonomisk (och mycket uppskattad!) Semestergåva till morföräldrar. Jag gjorde 5 kalendrar i år för mindre än $ 7 styck. Material: 12 fina bilder på ditt barn, barn, syskonbarn, brorson, hundar, katter eller andra släktingar 12 olika bitar