Innehållsförteckning:

- Författare John Day day@howwhatproduce.com.

- Public 2024-01-30 12:45.

- Senast ändrad 2025-01-23 15:11.

Målet med detta projekt är att skapa bildvisningsfunktionen för en Smart Mirror. Spegeln kan visa prognoser (soligt, delvis soligt, molnigt, blåsigt, regn, åska och snö) och temperaturvärden från -9999 ° till 9999 °. Prognos- och temperaturvärden är hårda kodade som för att efterlikna dem som analyseras från ett väder -API.

Projektet använder ett Zynq-Zybo-7000-kort som kör FreeRTOS och använder Vivado 2018.2 för att designa och programmera hårdvaran.

Delar:

Zynq-Zybo-7000 (med FreeRTOS)

19 LCD (640x480)

VGA -kabel

12 "x 18" akrylspegel

Steg 1: Konfigurera Vivado

Ladda ner Vivado 2018.2 från Xilinx och använd Webpack -licensen. Starta Vivado och "Skapa nytt projekt" och ge det ett namn. Välj sedan "RTL -projekt" och markera "Ange inte källor just nu." När du väljer en del väljer du "xc7z010clg400-1" och träff "Slutför" på nästa sida.

Steg 2: Förpackning av VGA -drivrutins -IP

Lägg till filen vga_driver.sv i designkällorna. Klicka sedan på "Verktyg" och välj "Skapa och paketera ny IP". Välj "Paketera ditt nuvarande projekt." Välj sedan en IP -plats och "Inkludera.xci -filer". Klicka på "OK" i popup -fönstret och sedan på "Slutför".

Gå till "Förpackningssteg" till "Granska och paketera" och välj "Paketets IP".

Nu ska vga_driver vara tillgänglig som ett IP -block.

Steg 3: Zynq IP

Under avsnittet "IP Integrator" väljer du "Skapa blockdesign". Lägg till "ZYNQ7 Processing System" och dubbelklicka på blocket. Klicka på "Importera XPS -inställningar" och ladda upp filen ZYBO_zynq_def.xml.

Under "PS-PL-konfiguration" öppnar du rullgardinsmenyn för "AXI Non Secure Enablement" och markerar "M AXI GP0-gränssnitt".

Därefter öppnar du rullgardinsmenyn för "Application Processor Unit" under "MIO -konfiguration" och markerar "Timer 0" och "Watchdog".

Slutligen, under "Clock Configuration" öppnar du rullgardinsmenyn för "PL Fabric Clocks" och markerar "FCLK_CLK0" och vid 100 MHz.

Steg 4: GPIO IP

Lägg till två GPIO -block till blockdesignen. GPIO: erna kommer att användas för att styra pixeladressen och RGB -komponenterna i pixlarna. Konfigurera blocken som visas på bilderna ovan. När du lägger till och konfigurerar båda blocken klickar du på "Kör anslutningsautomation".

GPIO 0 - Kanal 1 styr pixeladressen och kanal 2 styr den röda färgen.

GPIO 1 - Kanal 1 styr den gröna färgen och kanal 2 styr den blå färgen.

Steg 5: Blockera minne

Lägg till en Block Memory Generator IP till Block Design och konfigurera enligt bilden ovan. Pixelfärgerna skrivs till minnesadresser som sedan läses av VGA -drivrutinen. Adressraden måste matcha antalet pixlar som används så den måste vara 16 bitar. Data i är också 16 bitar eftersom det finns 16 färgbitar. Vi bryr oss inte om att läsa några kvitteringsbitar.

Steg 6: Annan IP

Den bifogade pdf -filen visar den färdiga Blockdesignen. Lägg till den saknade IP -adressen och slutför anslutningarna. Också "Make Externals" för VGA -färgutgångarna och de vertikala och horisontella synkroniseringsutgångarna.

xlconcat_0 - sammanfogar de enskilda färgerna för att bilda en 16 -bitars RGB -signal som matas in i block -RAM.

xlconcat_1 - sammanfogar kolumn- och radsignalerna från VGA -drivrutinen och matas in i port B i block -RAM. Detta gör att VGA -drivrutinen kan läsa pixelfärgvärden.

VDD - konstant HÖG ansluten till skrivfunktionen för block -RAM så att vi alltid kan göra det.

xlslice_0, 1, 2 - Skivorna används för att bryta RGB -signalen till individuella R-, G- och B -signaler som kan matas in i VGA -drivrutinen.

När blockdesignen är klar genererar du en HDL -omslag och lägger till begränsningsfilen.

*Blockdesign är baserad på självstudien skriven av benlin1994*

Steg 7: SDK

Koden som kör denna blockdesign ingår nedan. Init.c innehåller de funktioner som hanterar ritningen (prognoser, siffror, gradersymbol, etc.). Huvudslingan i main.c är det som körs när styrelsen är programmerad. Denna slinga anger prognos- och temperaturvärden och anropar sedan dragfunktionerna i init.c. Den går för närvarande igenom alla sju prognoserna och visar den ena efter den andra. Det rekommenderas att du lägger till en brytpunkt på rad 239 så att du kan se varje bild. Koden kommenteras och ger dig mer information.

Steg 8: Slutsats

För att förbättra det aktuella projektet skulle man kunna ladda upp prognosbilder i förväg i form av COE -filer till Block Memory Generators. Så istället för att rita prognoserna manuellt som vi gjorde i C -koden, kunde man få bilderna inlästa. Vi försökte göra detta men kunde inte få det att fungera. Vi kunde läsa pixelvärden och mata ut dem men det skapade röriga bilder som inte liknade dem vi laddade upp till RAM -minnet. Block Memory Generator -databladet är användbart att läsa.

Projektet är i huvudsak en halv Smart Mirror eftersom det saknar internetanslutningsaspekten. Att lägga till detta skulle ge en komplett Smart Mirror.

Rekommenderad:

Arduino Car Reverse Parking Alert System - Steg för steg: 4 steg

Arduino Car Reverse Parking Alert System | Steg för steg: I det här projektet kommer jag att utforma en enkel Arduino Car Reverse Parking Sensor Circuit med Arduino UNO och HC-SR04 Ultrasonic Sensor. Detta Arduino -baserade bilomvändningsvarningssystem kan användas för autonom navigering, robotavstånd och andra

Steg för steg PC -byggnad: 9 steg

Steg för steg PC -byggnad: Tillbehör: Hårdvara: ModerkortCPU & CPU -kylarePSU (strömförsörjningsenhet) Lagring (HDD/SSD) RAMGPU (krävs inte) CaseTools: Skruvmejsel ESD -armband/mathermisk pasta med applikator

Tre högtalarkretsar -- Steg-för-steg handledning: 3 steg

Tre högtalarkretsar || Steg-för-steg-handledning: Högtalarkretsen förstärker ljudsignalerna som tas emot från miljön till MIC och skickar den till högtalaren varifrån förstärkt ljud produceras. Här visar jag dig tre olika sätt att göra denna högtalarkrets med:

Steg-för-steg-utbildning i robotik med ett kit: 6 steg

Steg-för-steg-utbildning i robotik med ett kit: Efter ganska många månader av att bygga min egen robot (se alla dessa), och efter att två gånger ha misslyckats med delar, bestämde jag mig för att ta ett steg tillbaka och tänka om min strategi och riktning. De flera månaders erfarenhet var ibland mycket givande och

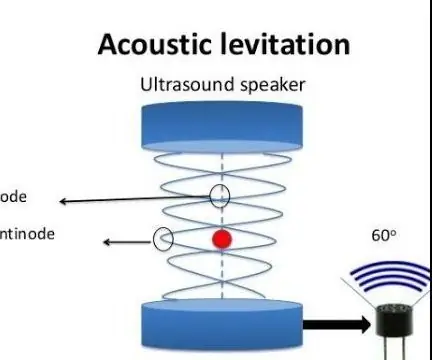

Akustisk levitation med Arduino Uno Steg-för-steg (8-steg): 8 steg

Akustisk levitation med Arduino Uno Steg-för-steg (8-steg): ultraljudsgivare L298N Dc kvinnlig adapter strömförsörjning med en manlig DC-pin Arduino UNOBreadboardHur det fungerar: Först laddar du upp kod till Arduino Uno (det är en mikrokontroller utrustad med digital och analoga portar för att konvertera kod (C ++)