Innehållsförteckning:

- Steg 1: Konfigurera Zynq programmerbar logik för sändare

- Steg 2: Konfigurera Zynq programmerbar logik för mottagare

- Steg 3: Konfigurera VDMA -drivrutinen

- Steg 4: Konfigurera Nanorouter -nätverk

- Steg 5: Installera Zynq Processing System för dataöverföring via Ethernet

- Steg 6: Installera Zynq Processing System för datamottagning via Ethernet

- Steg 7: Anslut dina Zybo -kort till HDMI -källan och HDMI -sinken

- Steg 8: Alternativa idéer för förbättring

- Steg 9: Tillgänglighet

- Författare John Day day@howwhatproduce.com.

- Public 2024-01-30 12:45.

- Senast ändrad 2025-01-23 15:11.

Har du någonsin önskat att du kunde ansluta din TV till en dator eller bärbar dator som en extern bildskärm, men ville inte ha alla dessa irriterande sladdar i vägen? Om så är fallet är den här självstudien bara för dig! Medan det finns några produkter ute som uppnår detta mål, är ett DIY -projekt mycket mer tillfredsställande och potentiellt billigare.

Detta koncept skiljer sig från produkter som chromecast, eftersom det är avsett att ersätta en HDMI -sladd som ansluts till en bildskärm istället för att vara en strömningsenhet.

Vårt projekt skapades som ett slutprojekt för en Real Time Operating Systems -kurs vid California State Polytechnic University, San Luis Obispo.

Målet med projektet är att använda två Digilent Zybo-kort för att fungera som det trådlösa kommunikationsgränssnittet mellan en HDMI-sändarenhet (PC, blu-ray, etc) till en HDMI-mottagande enhet (Desktop Monitor, Projector, TV, etc).

En Digilent Zybo kommer att anslutas via HDMI till den överförande enheten, och den andra kommer att anslutas via HDMI till den mottagande enheten.

Den trådlösa kommunikationen kommer att ske med hjälp av ett trådlöst lokalt nätverk som är dedikerat till sändaren och mottagaren, utan att dirigeras via en hemrouter eller annan sådan enhet. Den trådlösa modulen som används för detta projekt är tplink wr802n nanorouter, varav en fungerar som en åtkomstpunkt för att etablera nätverket och den andra för att fungera som en klient för att ansluta till nätverket. Varje nanorouter kommer att anslutas via ethernetkabel till endera Zybo -kortet. När de är anslutna till dessa routrar kommer enheterna att kommunicera via TCP som om de var anslutna med en enda Ethernet -kabel (vilket betyder att den enda konfiguration som behövs för att upprätta en anslutning är klientens IP -adress).

Även om målet med projektet var att underlätta en ström av 1080x720 video @ 60Hz, var detta inte möjligt på grund av begränsningar i bandbredd i det trådlösa nätverket och bristen på realtidskomprimering för att minska data som krävs för att skicka. I stället fungerar detta projekt som ramarna för framtida utveckling för att uppnå detta mål, eftersom det har kraftigt begränsade begränsningar i bildhastighet för att korrekt strömma HDMI -data som avsett.

Projektkrav:

2x Digilent Zybo Development Boards (måste ha minst en HDMI -port)

2x HDMI -kablar

2x mikrousb -kablar (för att ansluta Zybo till PC för utveckling)

2x tplink wr802n nanorouters (inklusive adtl. 2x microusb och vägguttag)

2x ethernetkablar

*** Obs: Denna handledning förutsätter bekantskap med Vivado -designpaketet och erfarenhet av att skapa ett nytt projekt och blockdesign. ***

Steg 1: Konfigurera Zynq programmerbar logik för sändare

Vår metod för att utveckla den programmerbara logiken för sändaren var att utföra en hdmi-till-hdmi-pass-through från PC för att övervaka med hjälp av två Video Direct Memory Access (VDMA) -block, ett för skrivning och ett för läsning.

Båda väljs för fritt körande, 3 bildbuffertläge (0-1-2). Eftersom videokärnan är optimerad för 60 bildrutor per sekund, betyder det att VDMA skriver eller läser till en ny bildruta var 16,67 ms i denna ordning: 0, 1, 2, 0, 1, 2, 0, 1, 2. DDR -minnesplatserna för varje ram är olika för de två VDMA: erna eftersom de inte längre är synkroniserade med varandra. Istället används en hårdvarutimer (TTC1), konfigurerad för 60 Hz, för att synkronisera förflyttningen av data mellan de två minnesplatserna.

Bilden ovan visar tre ramar, deras dimensioner och mängden minne som var och en kräver (till höger om ramen). Om vi tilldelar skriv -VDMA till dessa minnesplatser kan vi tilldela lästa VDMA -minnesplatser bortom den här uppsättningen, säg börjar med 0x0B000000. Varje bildruta består av 1280*720 pixlar och varje pixel består av 8 bitar rött, grönt och blått för totalt 24 bitar. Det betyder att en ram består av 1280*720*3 byte (2,76 MB).

Inuti timern IRQ, som beskrivs i VDMA -drivrutinsinställningarna, hanterar kopiering av data mellan de två VMDA -minnesplatserna. VDMA ger en pekare till den aktuella ramen som skrivs till eller läses från. Ramen representeras av en särskild grå kod, som konverteras till programvara. De grå koddefinitionerna för en konfiguration med tre rambuffertar finns i AXI VDMA-produktguiden i bilaga C.

Detta gör att vi kan kopiera innehållet som skrivs till minnet utan att läsa från en ram som för närvarande skrivs till.

*** Observera att den lästa VDMA inte används när data skickas över det trådlösa nätverket. Det enda syftet är att verifiera att kopieringsminnet fungerar korrekt från skriv -VMDA. Läs VMDA bör inaktiveras. ***

Här är stegen för att skapa sändardesignblocket:

- När du skapar ett nytt projekt är det en bra idé att tilldela ett chip eller ett kort till projektet. Den här länken beskriver hur du lägger till nya kortfiler i Vivado -katalogen och kopplar rätt kort till ditt projekt. Det kommer att vara praktiskt när du lägger till Processing -blocket och övergår från hårdvara till programvara (SDK -sida).

-

Lägg till följande block:

- dvi2rgb

- Video in till Axi4-stream

- Timing Controller

- axi4-stream att vid ut

- rgb2dvi

- AXI VDMA x2

- AXI GPIO x2

- Klockguiden

- Konstant

- Zynq Processing System

- När du lägger till bearbetningssystemet klickar du på "Kör blockautomatisering" i den övre grönfärgade fältet och ser till att alternativet "Apply Board Preset" är valt. Lämna allt annat som standard.

- Bilder av varje blockkonfigurationsfönster finns i bilderna ovan. Om du inte ser en bild för ett visst fönster, lämna det bara som standard.

-

Börja konfigurera Zynq -bearbetningssystemet:

- I PS-PL-konfiguration AXI Non Secure Enable GP Master AXI, aktivera M AXI GP0-gränssnitt

- I PS-PL Configuration HP Slave AXI Interface, aktivera både HP0 och HP1

- I MIO -konfigurationen Se till att ENET0 är aktiverat under I/O -kringutrustning, sedan Application Processor Unit, aktivera Timer0

- I Clock Configuration PL Fabric Clocks, aktivera FCLK_CLK0 och ställ in på 100 MHz.

- Klicka på Ok

- Innan du klickar på "Kör anslutningsautomatisering", var noga med att ansluta videoblocken enligt bilden i TX -blockets design ovan. Du kommer att vilja byta namn på konstanten till VDD och ställa in värdet till 1. Anslut videoblocken i enlighet därmed.

- Gör HDMI TMDS -klockan och datastiften externa på rgb2dvi- och dvi2rgb -blocken

- Skapa en ingångs- och utgångsport för hot plug -detektionssignalen (HPD) och anslut dem, dessa definieras i begränsningsfilen

-

Pixelklockan återställs från TMDS_Clk_p, som skapas i begränsningsfilen. Detta kommer att vara 74,25 MHz i enlighet med 720p upplösning. Det är viktigt att ansluta pixelklockan (från dvi2rgb -blocket) till följande stift:

- vid_io_in_clk (vid in till axi stream block)

- vid_io_out_clk (axi stream to vid out block)

- clk (Timing Controller)

- PixelClk (rgb2dvi)

- *** Obs! För närvarande för att aktivera pixelklockåterställningen måste HDMI rx- och tx -kontakterna vara anslutna till en aktiv källa/diskbänk. En väg runt detta är att separera video rx- och tx -blocken till olika klockdomäner (med andra ord, skapa en ny 74,25 MHz klocka för att mata till tx -blocket). ***

- Ställ sedan in klockguiden så att du har en 100 MHz ingång (global buffertkälla) och 3 utgångsklockor @ 50 MHz (AXI-Lite klocka), 150 MHz (AXI4-Stream klocka), 200 MHz (dvi2rgb RefClk pin).

- Anslut stiftet FCLK_CLK0 -processystem till ingången för klockguiden

- Klicka på "Kör anslutningsautomatisering" från den gröna stapeln högst upp i designfönstret. Det är en bra idé att göra detta för ett block i taget och följa TX -blockets designbild ovan.

- Verktyget kommer att försöka lägga till AXI-anslutningen, som fungerar som master/slav-sammankoppling för blocken som använder AXI-Lite-bussen (VDMA och GPIO).

- Det kommer också att lägga till AXI SmartConnect, som fungerar som master/slave-anslutning för AXI4-Stream- och High Performance-processorgränssnitt som används av VDMA (Stream to Memory Map och vice versa).

- Verktyget lägger också till en processorsystemåterställning. Se till att detta endast är anslutet till VDMA, GPIO och processorrelaterade block. Anslut den inte till några videoblock (dvs. dvi2rgb, timing controller, vid to stream etc.)

- När anslutningsautomatiseringen är klar kontrollerar du att anslutningarna stämmer överens med TX -blockdesignavbildningen. Du kommer att märka ett extra System ILA -block som inte har nämnts. Detta är endast för felsökning och behövs inte för tillfället. Den använder 150M Processor Reset, så det behövs inte heller. Var som helst du ser små gröna "buggar" på bussar, det är på grund av ILA och kan ignoreras.

- Det sista steget är att högerklicka på blockdesignen i trädet för projektkällor och välja "Skapa HDL -omslag." Om du planerar att lägga till logik i omslaget kommer det att skrivas över varje gång detta väljs.

- Se avsnittet VDMA -drivrutinsinställningar för mer information om SDK -sidan.

Klockor och återställningar

Jag har funnit att de viktigaste aspekterna av alla programmerbara logikprojekt är noggrann övervägande av klockdomäner och återställningssignaler. Om de är korrekt konfigurerade har du ett bra skott på att få din design att fungera.

Pixel Clock och Timing låst

För att verifiera att vissa signaler är aktiva är det en bra idé att knyta dessa signaler till lysdioder (klockor, återställningar, lås etc). Två signaler som jag tyckte var bra att spåra på sändarkortet var pixelklockan och den "låsta" signalen på AXI4-Stream to video out-blocket, som berättar att videotimingen har synkroniserats med tidtagaren och videokällan data. Jag har lagt till lite logik i designblocket, som spårar pixelklockan med PixelClkLocked -signalen på dvi2rgb -blocket som en återställning. Jag har bifogat filen som hdmi_wrapper.v här. Begränsningsfilen bifogas också här.

Steg 2: Konfigurera Zynq programmerbar logik för mottagare

Det programmerbara logikblocket för mottagaren är enklare. Den viktigaste skillnaden, förutom de saknade hdmi -ingångsblocken, är frånvaron av en återställd pixelklocka. Av den anledningen måste vi skapa vår egen från klockguiden. Denna design bör göras i ett separat projekt från sändaren. För våra ändamål följde mottagarprojektet Zybo 7Z-20-kortet medan sändaren följde Z7-10-kortet. FPGA: erna på brädorna är olika så … var försiktig.

Här är stegen för att skapa mottagarens designblock:

-

Lägg till följande ip -block i din design:

- Timing Controller

- AXI4-Stream till Video Out

- RGB till DVI

- AXI VDMA

- AXI GPIO

- Bearbetningssystem

- Klockguiden

- Konstant (VDD inställd på 1)

- Följ samma mönster för att konfigurera dessa block som sändaren. Bilder för de anmärkningsvärda skillnaderna i konfiguration har inkluderats här. De andra förblir desamma som sändaren.

- Konfigurera VDMA för denna design som läskanal. Inaktivera skrivkanalen.

-

Klockguiden bör konfigureras för följande utgångar:

- clk_out1: 75 MHz (pixelklocka)

- clk_out2: 150 MHz (strömklocka)

- clk_out3: 50 MHz (axi-lite klocka)

- Anslut videoblocken som visas i RX -blockdesignbilden.

- Kör sedan anslutningsautomatiseringen, vilket lägger till blocken AXI Interconnect, AXI SmartConnect och System Reset och försöker göra lämpliga anslutningar. Gå långsamt hit för att se till att det inte utför oönskade anslutningar.

- Gör HDMI TMDS -klockan och datastiften externa på rgb2dvi -blocket

- Inget behov av hot plug -signal på denna design.

Steg 3: Konfigurera VDMA -drivrutinen

Installationen för de olika blocken som konfigureras via AXI-Lite-gränssnittet görs bäst genom att använda demoprojekt som ingår i BSP som referens. Efter att du har exporterat designhårdvaran och startat SDK från Vivado, vill du lägga till ett nytt kortstödspaket och inkludera lwip202 -biblioteket i fönstret BSP -inställningar. Öppna system.mss -filen från BSP så ser du de perifera drivrutinerna från din blockdesign. Med alternativet "Importera exempel" kan du importera demoprojekt som använder dessa kringutrustning och därmed visa dig hur du konfigurerar dem i programvara med hjälp av tillgängliga Xilinx -drivrutiner (se bifogad bild).

Detta var metoden som användes för att konfigurera VDMA, Timer & Interrupt och GPIO. Källkoden för både sändning och mottagning har inkluderats här. Skillnaderna är nästan uteslutande i main.c.

*** OBS: Eftersom systemet inte är fullt fungerande när du skriver den här självstudien innehåller källkoden i det här avsnittet inte den trådlösa nätverkskoden. Flera buggar måste åtgärdas som ett resultat av att kombinera videokärnans sändnings-/mottagningsprojekt med nätverksöverförings-/mottagningsprojekt. Därför behandlar denna handledning dem separat för tillfället. ***

TX Interrupt Handler -funktion (IRQHandler)

Denna funktion läser de grå koder som tillhandahålls av både läs- och skriv -VDMA: erna via GPIO -blocken. De grå koderna konverteras till decimal och används för att välja rambasminnesplats för den aktuella ramen. Ramen som kopieras är den föregående ramen till den som skrivs till av VDMA (t.ex. om VDMA skriver till ram 2 kopierar vi ram 1; om vi skriver till ram 0 lindar vi och läser från ram 2).

Funktionen fångar bara var sjätte bildruta för att minska bildhastigheten till 10 Hz snarare än 60 Hz. Den övre gränsen för nätverket är 300 Mbps. Vid 10 bilder per sekund krävs en bandbredd på 221,2 Mbps.

Genom att kommentera/avmarkera två rader i den här funktionen kan användaren byta till HDMI-passsthru-läge för felsökning/teständamål (koden kommenteras för att indikera lämpliga rader). Den kopierar för närvarande ramen till en minnesplats som används av ethernet -koden.

RX Interrupt Handler -funktion (IRQHandler)

Denna funktion är mycket lik TX -funktionen, men den kopierar från en FIFO med två buffertar som används av Ethernet för att skriva inkommande data till. Ethernet -koden indikerar vilken ram som skrivs till av FIFO, data kopieras från den motsatta ramen. Data kopieras till ramen direkt bakom den som läses av VDMA för att undvika rivning.

Steg 4: Konfigurera Nanorouter -nätverk

För att skapa ett nätverk med TPlink nanorouters, slå på dem individuellt och anslut till standard wifi -SSID för enheterna. Mer information om konfigurationsinställningarna för just denna enhet finns i enhetens användarhandbok.

Konfigurera en av enheterna som en åtkomstpunkt, den fungerar som den primära anslutningen för nätverket. Se till att namnge nätverket och anteckna namnet och inaktivera DHCP (vi vill inte att routern ska konfigurera IP -adresserna dynamiskt, vi vill att tändsändaren och mottagarens Zybo -kort ska ställa in sina IP -adresser själva så att de är konsekventa). Efter konfigurationen, se till att enheten startar om och upprättar detta nätverk.

Konfigurera den andra enheten som en klient och se till att den ansluter till nätverks -SSID som du konfigurerade med den första nanoroutern. Återigen, se till att DHCP är inaktiverat för klienten.

När klienten har slutfört och startat om bör den ansluta till åtkomstpunkten nanorouter (om den inte gör det är det troligtvis ett problem i konfigurationen av en av enheterna). Du kommer att märka att LED -lampan på klienten kommer att lysa fast när den har anslutit till åtkomstpunkten.

Nanorouter -lampan för åtkomstpunkten kommer sannolikt att fortsätta blinka vid denna tidpunkt, det här är okej! Den blinkande lampan betyder att den inte är ansluten till en annan enhet från dess Ethernet -port, och när den är ansluten till en konfigurerad Zybo kommer lysdioden att förbli fast för att indikera en lyckad nätverksanslutning.

Nu när vi har våra nanorouters -inställningar har vi ett trådlöst nätverk som gör att vi kan kommunicera igenom. En viktig anmärkning är att vår konfigurationsmetod för nanorouters (som åtkomstpunkt och klient) gör att vi kan kommunicera från det sändande Zybo -kortet till det mottagande Zybo -kortet som om de två var anslutna med en enda ethernetråd. Detta gör vår nätverksinställning mindre svår, eftersom alternativet sannolikt skulle innehålla konfigurering av Zybo -korten för att ansluta till servern uttryckligen tillsammans med den avsedda anslutningen.

När båda enheterna har konfigurerats är nanorouters konfigurerade och redo att implementeras i ditt WIDI -nätverk. Det finns ingen specifik parning mellan nanorouters och Zybo -korten, eftersom antingen åtkomstpunkten eller klienten fungerar för antingen sändnings- eller mottagningsenheten.

Steg 5: Installera Zynq Processing System för dataöverföring via Ethernet

För att överföra HDMI -data från ett Zybo -kort till det andra måste vi införliva ett Ethernet -protokoll med vår VDMA -drivrutin. Vårt mål här är att strömma enskilda videoramar via Ethernet -kringutrustningen i processystemet, med en bestämd hastighet som överensstämmer med vår nätverksbandbredd. För vårt projekt använde vi TCP från LwIP API för bara metall. Eftersom båda projektmedlemmarna är relativt oerfarna med nätverksverktyg, gjordes detta val utan att fullt ut inse konsekvenserna och begränsningarna med TCP. Det största problemet med denna implementering var den begränsade bandbredden och det faktum att den verkligen inte är utformad för ångande av stora datamängder. Alternativa lösningar för att ersätta TCP och förbättra tbe i detta projekt kommer att diskuteras senare.

En kort beskrivning av TCP med LwIP: Data skickas över nätverket i paket med storleken tcp_mss (TCP maximal segmentstorlek), vilket i allmänhet är 1460 byte. Att ringa tcp_write kommer att ta vissa data som refereras av en pekare och konfigurera pbufs (paketbuffertar) för att lagra data och ge en struktur för TCP -operationerna. Den maximala datamängden som kan köas samtidigt är inställd på tcp_snd_buf (TCP -avsändarbuffertutrymme). Eftersom denna parameter är ett 16 -bitars tal är vi begränsade till en sändningsbuffertstorlek på 59695 byte (det krävs viss vaddering i sändningsbufferten). När data har köats kallas tcp_output för att börja överföra data. Innan du skickar nästa datasegment är det absolut nödvändigt att alla tidigare paket har överförts framgångsrikt. Denna process utförs med hjälp av recv_callback -funktionen, eftersom detta är funktionen som kallas när kvitteringen ses från mottagaren.

Att använda exempelprojekten i Vivado SDK är till stor hjälp för att lära sig hur LwIP TCP -operationen är, och är en bra utgångspunkt för att starta ett nytt projekt.

Proceduren för WiDi -överföringsenheten är följande:

- Initiera TCP-nätverket med LWIP-drivrutinsfunktionssamtal av bara metall.

- Ange eventuella återuppringningsfunktioner som behövs för nätverksoperationer.

- Anslut till WiDi -mottagaren genom att ansluta till dess IP -adress och port (vår konfiguration: Mottagarens IP är 192.168.0.9, anslut till port 7).

- När VDMA -drivrutinens timer går ut anger du TX ISR.

- Bestäm den aktuella rambufferten för åtkomst baserat på den grå VDMA -koden

- Köa upp det första datasegmentet i TCP -sändningsbufferten

- Mata ut data och uppdatera lokala variabler för att hålla reda på hur mycket data som har skickats från den aktuella ramen.

- När du har nått den mottagna återuppringningen (funktionssamtal som görs efter att sändaren har fått ett kvitto på datahämtning), köar du nästa segment av data.

- Upprepa steg 7 och 8 tills hela ramen har skickats.

- Återgå till viloläge för att vänta på nästa timeravbrott för att indikera att en ny ram är klar (Tillbaka till steg 4).

Se till att konfigurera LwIP -inställningarna för kortstödspaketet som visas på bilden ovan. Alla värden är standard utom tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg. Observera också att detaljerad felsökning kan uppnås genom att ändra BSP -parametrarna för gruppen debug_options.

Steg 6: Installera Zynq Processing System för datamottagning via Ethernet

Zybo -utvecklingskortet som fungerar som den trådlösa mottagaren fungerar på samma sätt som den överförande enheten. Paketinställningarna för LwIP kommer att vara identiska med de i föregående steg.

Enheten kommer att ta in paket som innehåller videoramsegmenten från nanorouter, och den kommer att kopiera videoramsdata till det tredubbla rambuffertutrymmet för det mottagande VDMA. För att undvika överskrivning av data används en dubbel databuffert (vi kallar nätverksbufferten) när du samlar in data från nanoroutern, så att nätverkstrafiken kan fortsätta att strömma in medan den föregående hela videoramen kopieras till VDMA -buffert.

Proceduren för WiDi -mottagningsenheten kräver två uppgifter, varav en tar emot ethernetdata och den andra kopierar videoramar från nätverksbufferten till VDMA: s trippelrambuffert.

Ethernet -mottagningsuppgift:

- Initiera TCP-nätverket med LWIP-drivrutinsfunktionssamtal med bara metall (konfiguration med IP-adress som sändaren kommer att ansluta till, 192.168.0.9 i vårt)

- Ange eventuella återuppringningsfunktioner som behövs för nätverksoperationer.

- Vid mottaget Ethernet -paket, kopiera paketdata till nuvarande nätverksbuffert, öka aktuell ackumulerad data.

- Om paketet fyller nätverksrambufferten fortsätter du till steg 5 och 6. I annat fall går du tillbaka till steg 3 för denna uppgift.

- signal att VDMA -trippelrambuffertuppgiften ska kopieras från den nyligen färdiga nätverksbufferten.

- Byt till den andra nätverksbufferten och fortsätt samla in data via ethernet.

- Viloläge tills ett nytt Ethernet -paket tas emot (steg 3).

Kopiera nätverksbuffert till VDMA triple frame buffer:

- När VDMA -drivrutintimern löper ut anger du RX ISR.

- Bestäm den aktuella rambufferten för åtkomst baserat på den grå VDMA -koden.

- Bestäm vilken nätverksbuffert som ska kopieras till VDMA -bufferten och kopiera data

Steg 7: Anslut dina Zybo -kort till HDMI -källan och HDMI -sinken

Anslut nu hdmi -kablarna för både mottagare och sändare, programmera FPGA: erna och kör processsystemet. Bildfrekvensen kommer sannolikt att vara mycket långsam, på grund av den enorma omkostnaden i LwIP -operationen och begränsad bandbredd. Om det finns några problem, anslut via UART och försök att identifiera eventuella varningar eller fel.

Steg 8: Alternativa idéer för förbättring

En stor fråga för detta projekt var mängden data som behövs för att skicka via wifi. Detta var förväntat, men vi underskattade den inverkan detta skulle ha och resulterade i mer bildserier på en skärm snarare än ett videoflöde. Det finns flera sätt att förbättra detta projekt:

- Videokomprimering i realtid. Komprimering av det inkommande videoflöden bild för bild skulle kraftigt minska mängden data som behövs för att skickas över nätverket. Helst skulle detta göras i hårdvara (vilket inte är en lätt uppgift), eller så kan det göras i programvara med hjälp av den andra ARM -kärnan för att köra en komprimeringsalgoritmer (detta skulle behöva ytterligare analys för att säkerställa att timingen fungerar). Det finns några öppen källkodskomponenter i realtid som vi hittade på webben, men en majoritet är IP.

- Implementering av Ethernet -strömmen i hårdvara, snarare än programvara. Det fanns massor av omkostnader på grund av bristen på utrymme för att köa utgående data i sändaren, på grund av begränsningen av segmentstorleken. En mycket effektivare process är att använda AXI Ethernet IP med en FIFO -buffert eller DMA för att mata in data i den. Detta skulle minska det extra bagaget från LwIP TCP och möjliggöra mer dataflöde.

Steg 9: Tillgänglighet

Den resulterande produkten av detta WiDi -projekt bör vara ett fullt integrerat, kompakt par enheter som en användare kan ansluta till vilken HDMI -källa som helst och sedan sänka videoflöden till en bildskärm med HDMI -funktion trådlöst. Enheterna skulle innehålla Zynq-7000 SoC som finns på Zybo-referenskortet och innehålla nätverkshårdvaran som finns i TP-Link nano-routrar. Helst skulle användaren kunna styra överföringsmodulen från en diskret plats inom måloperativsystemet, med litet behov av betydande teknisk förmåga.

Säkerhet och anslutning

Enheterna bör också innehålla Transport Layer Security (TLS) och ha begränsad automatisk anslutningsförmåga, båda för sekretessändamål. Det är designernas avsikt att göra anslutningen med en display över ett trådlöst gränssnitt till en avsiktlig åtgärd för användarens räkning för att undvika att felaktigt sända känsligt material.

Nuvarande status

Fram till denna tid är projektets tillstånd fortfarande mycket på gång. För att den nuvarande slutpunktsanvändaren ska kunna dra nytta av denna handledning måste han eller hon ha en stark teknisk förståelse för inbäddad systemdesign och ha en viss kunskap om programmerbar maskinvara och inbäddad programvara som arbetar tillsammans.

Data som skickas över nätverket är inte krypterade vid denna tidpunkt och antas vara en rå överföring av TCP/IP -paket.

Videokärnprojektet testades framgångsrikt för både sändning och mottagning. Å andra sidan upprättades den trådlösa anslutningen mellan två zybo -kort och testramdata skickades framgångsrikt. Det är dock fortfarande nödvändigt att kombinera nätverkskoden till varje videokärnprojekt och testa överföringen av faktiska videoramar.

Rekommenderad:

DIY ESP32 Development Board - ESPer: 5 steg (med bilder)

DIY ESP32 Development Board - ESPer: Så nyligen hade jag läst om många IoT (Internet of Things) och lita på mig, jag kunde bara inte vänta med att testa en av dessa underbara enheter, med möjlighet att ansluta till internet, mig själv och få tag på jobbet. Lyckligtvis är möjligheten att

JALPIC One Development Board: 5 steg (med bilder)

JALPIC One Development Board: Om du följer mina Instructables -projekt vet du att jag är ett stort fan av programmeringsspråket JAL i kombination med PIC Microcontroller. JAL är ett Pascal-liknande programmeringsspråk som utvecklats för 8-bitars PIC-mikrokontroller av Microchip. Mo

Designa en Microcontroller Development Board: 14 steg (med bilder)

Designa en Microcontroller Development Board: Är du en tillverkare, hobbyist eller hacker som är intresserad av att ta steget från perfboard -projekt, DIP IC och hemmagjorda PCB till flerskiktade PCB tillverkade av styrelsehus och SMD -förpackningar redo för massproduktion? Då är det här instruerbart för dig! Den här gui

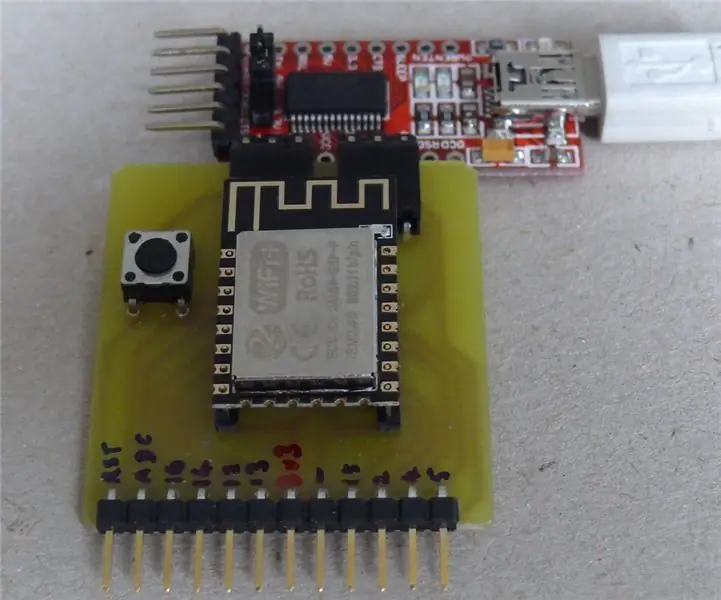

ESP-12E och ESP-12F Programming and Development Board: 3 steg (med bilder)

ESP-12E och ESP-12F programmerings- och utvecklingsnämnd: Uppdraget för detta kort var enkelt: Kunna programmera ESP-12E och ESP-12F-moduler lika enkelt som NodeMCU-korten (det vill säga inget behov av att trycka på knapparna). Ha brödbräda -vänliga stift med tillgång till den användbara IO. Använd en separat USB till seriell konvertering

Quadcopter med Zybo Zynq-7000 Board: 5 steg

Quadcopter Använda Zybo Zynq-7000 Board: Innan vi sätter igång, här är några saker du vill ha för projektet: Dellista1x Digilent Zybo Zynq-7000 board 1x Quadcopter Frame som kan monteras Zybo (Adobe Illustrator-fil för laserskärning bifogad) 4x Turnigy D3530/ 14 1100KV borstlösa motorer 4x