Innehållsförteckning:

- Författare John Day day@howwhatproduce.com.

- Public 2024-01-30 12:42.

- Senast ändrad 2025-01-23 15:11.

Vårt mål med detta projekt var att skapa något som skulle spara samhällen energi och ekonomiska resurser. Rörelseaktiverade gatubelysning skulle göra båda dessa saker. Över hela landet slösas energi bort på gatubelysning som tänder gator som är tomma. Vårt gatubelysningssystem säkerställer att lamporna bara är tända vid behov, vilket sparar samhällen otaliga dollar. Med hjälp av rörelsesensorer tänder systemet bara lampor när bilar är närvarande. Även för fotgängares säkerhet implementerade vi en överstyrningsknapp som tänder alla lampor på gatan. Följande steg kommer att leda dig igenom hur vi utformade och byggde vår nedskalade modell av projektet med Vivado och en Basys 3 -tavla.

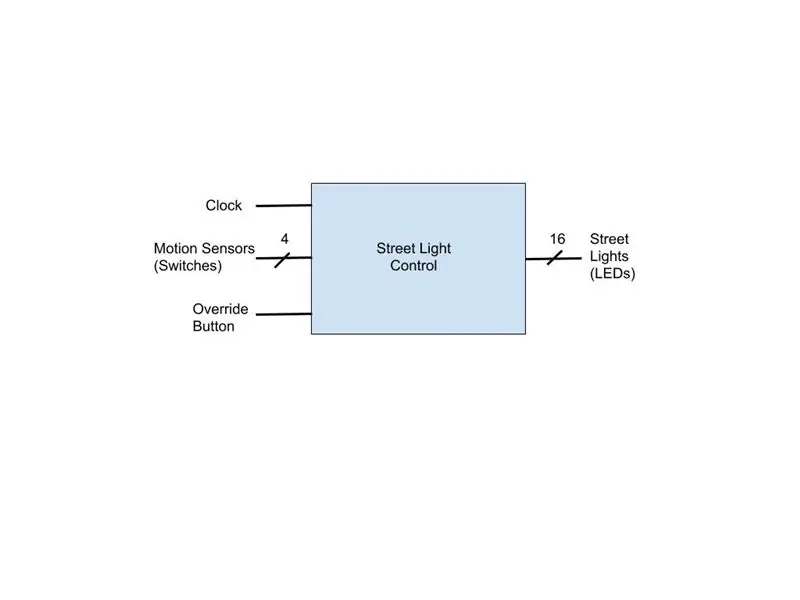

Steg 1: System Black Box

Vi började detta projekt med att rita ett enkelt svart lådediagram. Ett svart lådediagram visar helt enkelt de ingångar och utgångar som vårt system kräver för att slutföra alla nödvändiga processer. Vi försökte hålla vår design så enkel och enkel som möjligt. Våra tre systemingångar inkluderade en buss med rörelsessensorer (4 för vår nedskalade modell), en övergångsknapp för fotgängare och en klockingång. På andra sidan är vår enda utgång en buss med LED -lampor som representerar våra gatubelysning. För den här modellen använde vi ett scenario med 16 gatubelysning helt enkelt för att det är det maximala antalet inbyggda LED -utgångar på Basys 3 -kortet. Slutligen, med hjälp av detta diagram kunde vi skapa våra Vivado -projekt, käll- och begränsningsfiler med lämpliga in- och utdata.

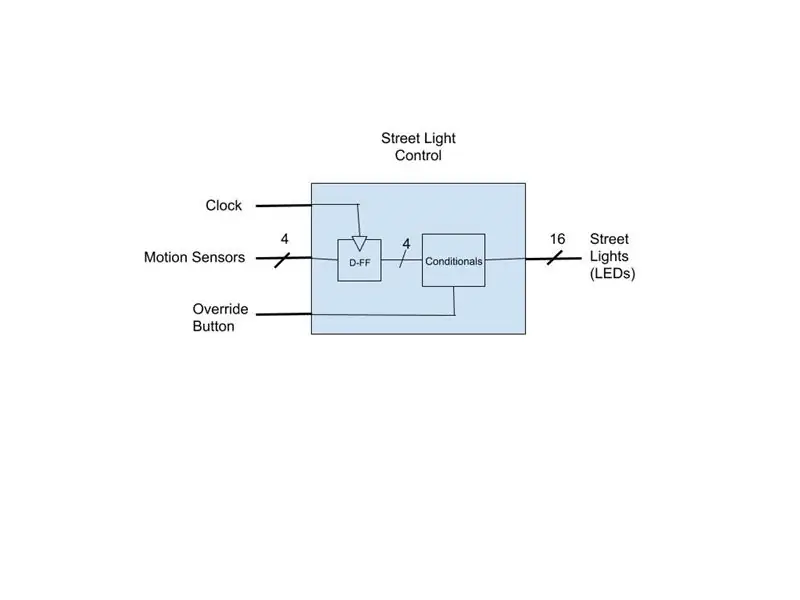

Steg 2: Komponenter

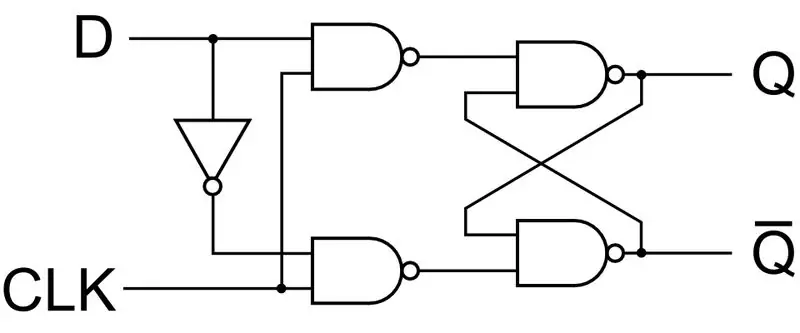

I det här steget dyker vi djupare och undersöker komponenterna i vårt black box -diagram. Vår första komponent är en VHDL-källfil som innehåller D-flip-flops. D flip-flops tar helt enkelt vilken signal som matas in till dem från sensorerna på klockans stigande kant och spärrar in data till nästa stigande kant. Detta hindrar våra känsliga rörelsesensorer från att orsaka att utgångs -lysdioderna "flimrar". Vi lägger också en enda D-vippa på knappens ingångssignal för att hålla lysdioderna tända i cirka 5-7 sekunder efter att knappen tryckts in. Vi körde också detta genom en klockavdelare.

enhet clk_div2 är Port (clk: in std_logic; sclk: out std_logic); avsluta clk_div2;

arkitektur my_clk_div av clk_div2 är

konstant max_count: heltal: = (300000000); signal tmp_clk: std_logic: = '0'; börja my_div: process (clk, tmp_clk) variabel div_cnt: heltal: = 0; börja om (rising_edge (clk)) sedan om (div_cnt = MAX_COUNT) sedan tmp_clk <= inte tmp_clk; div_cnt: = 0; annars div_cnt: = div_cnt + 1; sluta om; sluta om; sclk <= tmp_clk; avsluta processen my_div; avsluta my_clk_div;

Vår sista komponent i detta diagram är en beteendemässig VHDL -källfil som innehåller villkor för utgångarna baserat på konfigurationen av insignaler.

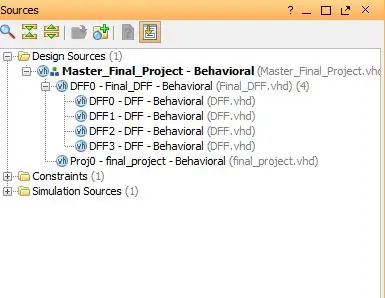

Steg 3: D Flip-flops

De fyra flip-flops som är anslutna till insignalerna är viktiga för funktionaliteten i vårt system. Som sagt tidigare, med känsliga rörelsessensorer och en överstyrningsknapp, använder vipporna spärrar för att bara mata ut vår insignal på klockans stigande kant. Denna sekventiella logik innebär att våra gatubelysning kan lysa under en viss tid efter att de har utlösts av en snabb rörelse. Kodningen för en D-Flip Flop är ganska enkel:

beginprocess (CLK) start if rising_edge (CLK) sedan Q <= D; sluta om; avsluta process;

Det hela kan sammanställas till ett enda if -uttalande. När vi väl hade den här biten skapade vi en strukturell VHDL-källfil som innehåller alla fyra av våra nödvändiga flip-flops:

börja DFF0: DFF -portkarta (CLK => CLK, D => D (0), Q => Q (0)); DFF1: DFF -portkarta (CLK => CLK, D => D (1), Q => Q (1)); DFF2: DFF -portkarta (CLK => CLK, D => D (2), Q => Q (2)); DFF3: DFF -portkarta (CLK => CLK, D => D (3), Q => Q (3));

slut Beteende;

Detta hjälper till att hålla vår huvudstrukturstruktur där vi sammanför alla systemkomponenter mycket mer rena och organiserade.

Steg 4: Villkor

För att hålla vår kod kompakt och effektiv skrev vi alla våra villkor i ett enda ärende. För vår nedskalade modell hade vi 16 möjliga LED -utgångskonfigurationer eftersom varje rörelsesensor ansvarar för en grupp om 4 lysdioder.:

fallet NMS är när "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED <= "1111111111111111"; slutfall;

Steg 5: Begränsningar

För att korrekt ange dina ingångar och utgångar med Vivado måste du implementera en begränsningsfil som anger alla portar, knappar, lysdioder och klockor som används.

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMOS33 [get_ports_ LED] U19 [get_ports {LED [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [2]}] set_property PACKAGE_PIN V19 [get_ports {LED [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [3]}] set_property PACK get_ports {LED [4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [4]}] set_property PACKAGE_PIN U15 [get_ports {LED [5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [5]}] set_prop_ PACKAGE_ LED [6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [6]}] set_property PACKAGE_PIN V14 [get_ports {LED [7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [7]}] set_property PACKAGE_PIN V13 [8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [8]}] set_property PACKAGE_PIN V3 [get_ports {LED [9]}] set_property IO STANDARD LVCMOS33 [get_ports {LED [9]}] set_property PACKAGE_PIN W3 [get_ports {LED [10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [10]}] set_property PACKAGE_PIN U3 [get_ports {LED [11] }OS_33] [get_ports {LED [11]}] set_property PACKAGE_PIN P3 [get_ports {LED [12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [12]}] set_property PACKAGE_PIN N3 [get_ports {LED [13]}] set_property IOST33 {LED [13]}] set_property PACKAGE_PIN P1 [get_ports {LED [14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [14]}] set_property PACKAGE_PIN L1 [get_ports {LED [15]}] set_property IOSTANDARD LVCMOS33 [15]}]

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

set_property PACKAGE_PIN A14 [get_ports {MS [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMOS33 [get_ports] [prop_PACK] B15 [get_ports {MS [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [2]}] set_property PACKAGE_PIN B16 [get_ports {MS [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [3]}]

Steg 6: Huvudkällfil

I denna huvudfil samlar vi alla komponentkällfiler som nämnts tidigare. Denna fil fungerar som strukturell kod som sammanför de olika komponenterna.

entitet Master_Final_Project är Port (BTN: i STD_LOGIC; CLK: i STD_LOGIC; MS: i STD_LOGIC_VECTOR (3 ner till 0); LED: ut STD_LOGIC_VECTOR (15 ner till 0)); avsluta Master_Final_Project;

arkitektur Beteende för Master_Final_Project är

komponent final_project är Port (--CLK: i STD_LOGIC; NMS: i STD_LOGIC_VECTOR (3 ner till 0); BTN: i STD_LOGIC; --sw: i STD_LOGIC_Vector (1 ner till 0); LED: ut STD_LOGIC_VECTOR (15 ner till 0)); slutkomponent;

komponent Final_DFF är

Port (CLK: i STD_LOGIC; D: i STD_LOGIC_Vector (3 ner till 0); Q: ut STD_LOGIC_Vector (3 ner till 0)); slutkomponent;

signal DFF02proj30: STD_LOGIC;

signal DFF12proj74: STD_LOGIC; signal DFF22proj118: STD_LOGIC; signal DFF32proj1512: STD_LOGIC;

Börja

DFF0: Final_DFF -portkarta (CLK => CLK, D (0) => MS (0), D (1) => MS (1), D (2) => MS (2), D (3) => MS (3), Q (0) => DFF02proj30, Q (1) => DFF12proj74, Q (2) => DFF22proj118, Q (3) => DFF32proj1512); Proj0: final_project port map (NMS (0) => DFF02proj30, NMS (1) => DFF12proj74, NMS (2) => DFF22proj118, NMS (3) => DFF32proj1512, BTN => BTN, LED => LED); slut Beteende;

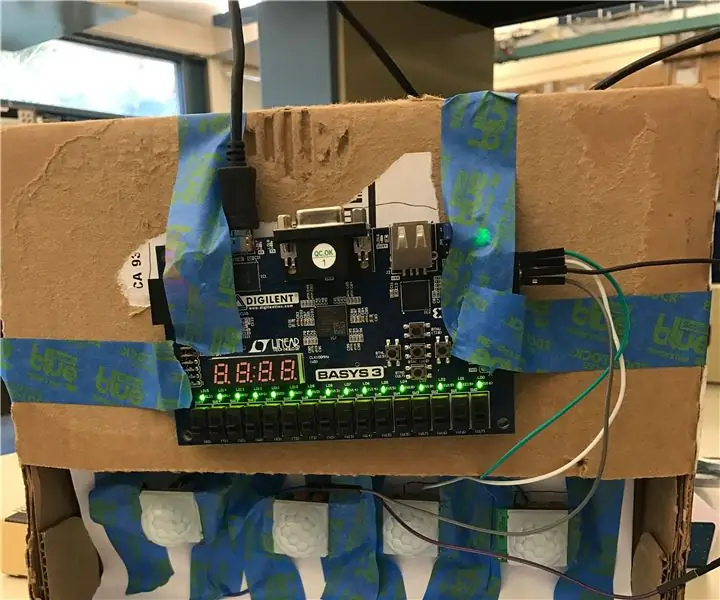

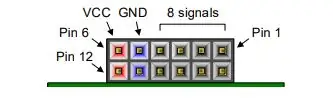

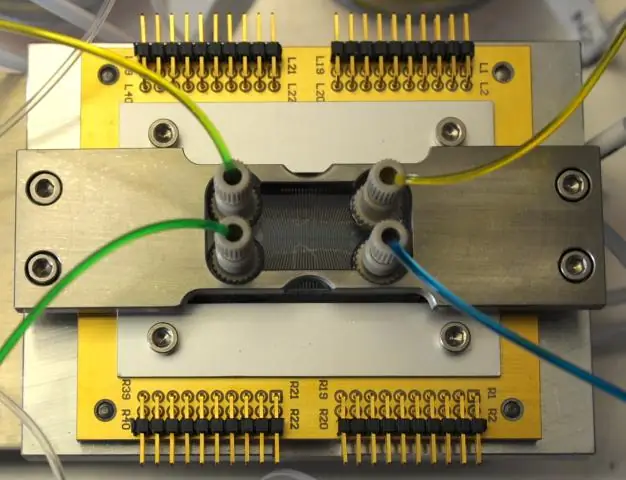

Steg 7: Montering

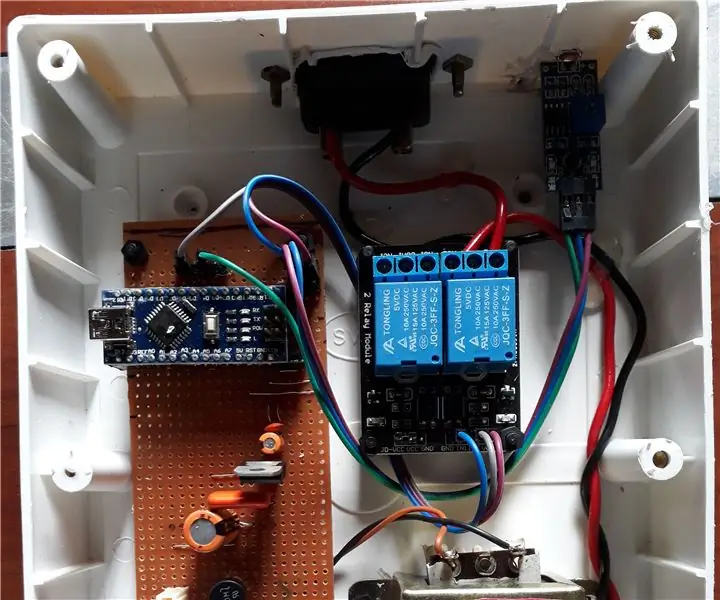

Hårdvaran för detta projekt är minimal. De enda bitarna som krävs är följande:

1. Basys 3 board (1)

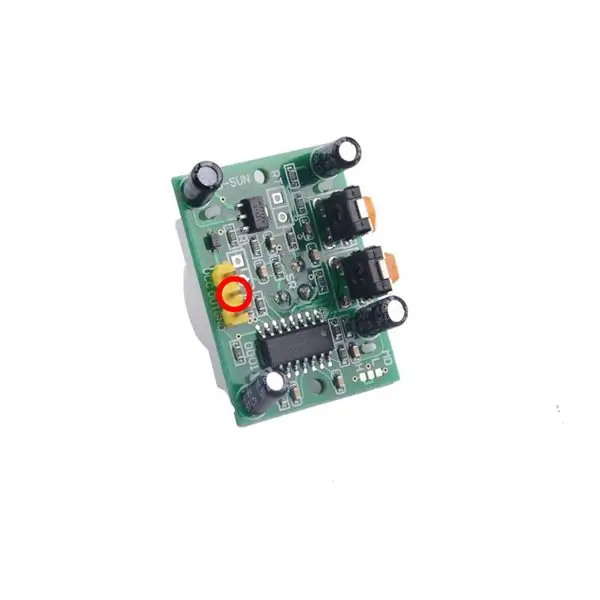

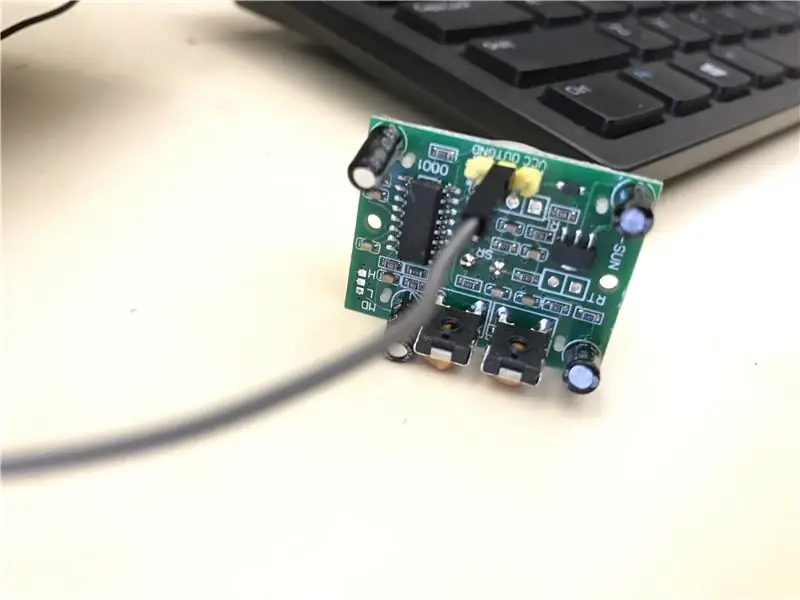

2. Billiga rörelsesensorer som finns på Amazon här. (4)

3. Man-till-hona leder (4)

Hopsättning:

1. Anslut fyra hanledningar till PMod-huvudets JB-portar 1-4 (se bild).

2. Anslut honändarna till varje rörelsesensors utgångsstift.

Steg 8: Läser in programmet

Nu är vi redo att ladda VHDL -huvudkällfilen till Basys 3 -kortet. Se till att köra syntes, implementering och generera bitströmskontroll efter eventuella fel. Om alla körs framgångsrikt öppnar du maskinvaruhanteraren och programmerar Basys 3 -enheten. Ditt projekt är nu klart!

Rekommenderad:

Rörelseaktiverad lampbrytare: 3 steg

Motion Activated Lamp Switch: När vi lämnar vårt skrivbord eller rum glömmer vi oftast att släcka lamporna där. Detta orsakar förlust av el och ökar din elräkning. Men vad händer om lamporna slocknar automatiskt när du lämnar rummet. Ja i

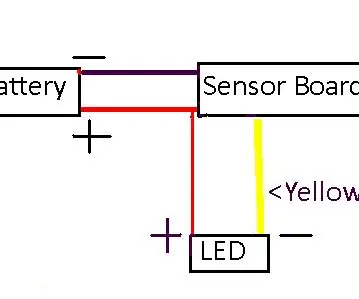

Batteridriven rörelseaktiverad LED-lampa: 4 steg

Batteridriven rörelse-aktiverad LED-lampa: Om du vill sätta en lampa någonstans som inte låter sig kopplas in kan det vara precis vad du behöver

Rörelseaktiverad ljusbrytare med ljussensor: 5 steg

Rörelseaktiverad ljusomkopplare med ljussensor: Rörelseaktiverad ljusomkopplare har många tillämpningar både hemma och på kontoret. Detta har dock ytterligare en fördel med att införliva en ljussensor, så att det här ljuset bara kan aktiveras på natten

Rörelseaktiverad Redstone: 7 steg (med bilder)

Rörelseaktiverad Redstone: Hej! Detta projekt är en rörelseaktiverad rödstenslampa. Det fungerar genom att använda en smula mikrokontroller och en ultraljudsavståndssensor som är ansluten till ett relä. Detta projekt deltar i minecraft -tävlingen och eventuella röster, favoriter eller sam

Energieffektiv dator: 9 steg

Energieffektiv dator: Det finns otaliga instruktioner och hur du artiklar på webben och trycker på att bygga din egen dator. Det finns dock inte så många guider för att bygga en dator som är energieffektiv. Under hela det här instruerbara ger jag dig några tips om hur du väljer