Innehållsförteckning:

- Steg 1: Block Diagram

- Steg 2: Funktionsprincip

- Steg 3: Logisk implementering

- Steg 4: Lösa dödläge

- Steg 5: Enhetskonfiguration - Matrix0 -krets

- Steg 6: Enhetskonfiguration - SPI Clocking Logic

- Steg 7: Enhetskonfiguration - Egenskaper för Matrix0 -komponenter

- Steg 8: Enhetskonfiguration - Matrix1 -krets

- Steg 9: Enhetskonfiguration - 3 -bitars binär räknare

- Steg 10: Enhetskonfiguration - 3 -bitars jämförelselogik

- Steg 11: Enhetskonfiguration - Digital jämför logik och tillfälligt register

- Steg 12: Enhetskonfiguration - Egenskaper för Matrix1 -komponenter

- Steg 13: Resultat

- Författare John Day day@howwhatproduce.com.

- Public 2024-01-30 12:39.

- Senast ändrad 2025-01-23 15:10.

Styrsystem och relaterade enheter hanterar flera strömkällor, såsom förspänningslinjer eller batterier, och måste spåra den högsta (eller lägsta) linjen bland en given uppsättning.

Till exempel kräver belastningsväxling i ett "multi-batteri" -drivet system att systemet övervakar antingen den lägsta eller maximala spänningen bland batterierna (max eller min som en funktion av den specifika kopplingsalgoritmen) och dynamiskt dirigerar lasten till lämpligaste källan i realtid. Alternativt kan systemet behöva tillfälligt koppla bort det lägsta spänningsbatteriet för korrekt laddning.

Ett annat exempel är det moderna solenergisystemet, där varje solpanel är utrustad med en tiltrotatmekanism och med en solspårningskrets (den senare ger information om solens position för att orientera panelen). Med information om maxspänningen kan varje solpanels position finjusteras på grundval av att strängens panel faktiskt levererar den högsta utspänningen och därmed uppnår en överlägsen nivå av effektoptimering.

Det finns flera olika märken av kommersiella IC: er (främst mikrokontroller) som i princip kan implementera en maxspänningsföljare. De kräver dock programmering och är mindre kostnadseffektiva än en blandningssignallösning. Att komplettera en Dialog GreenPAKTM -design kan positivt påverka designens överkomlighet, storlek och modularitet. Denna design utnyttjar fördelen med att integrera både analoga och digitala kretsar i ett enda chip.

I denna instruktionsbok implementeras den analoga fronten och den digitala logiken som krävs för att implementera en max (eller så småningom min) spänningssökare bland åtta olika källor.

För att implementera den 8-kanals analoga max/min spänningsmonitorn används en SLG46620G.

Nedan beskrivs stegen som behövs för att förstå hur lösningen har programmerats för att skapa 8-kanals analog max/min spänningsmonitor. Men om du bara vill få resultatet av programmeringen, ladda ner GreenPAK -programvara för att se den redan färdiga GreenPAK -designfilen. Anslut GreenPAK Development Kit till din dator och tryck på programmet för att skapa 8-kanals analog max/min spänningsmonitor.

Steg 1: Block Diagram

Figur 1 visar det globala diagrammet över det implementerade systemet.

En sträng med upp till 8 variabla spänningskällor multiplexeras och gränssnitts till en GreenPAKs ADC -modul ansluten till en anpassad intern design som kan välja källan med den högsta spänningen i förhållande till de andra. Den interna logiken matar ut denna information för visning eller vidare behandling.

Designen är baserad på GreenPAK SLG46620G -produkten, eftersom den innehåller alla nödvändiga analoga och digitala byggstenar för applikationen. I denna implementering skannas arrayen med hjälp av en ADG508 analog multiplexer direkt driven av GreenPAK IC.

Utgångsinformationen är ett 3-bitars digitalt tal som motsvarar spänningskällans nummer vid max spänning. Ett direkt sätt att få denna information är att visa numret med hjälp av en 7-segmentskärm. Det kan enkelt uppnås genom att ansluta SLG46620G: s digitala utgång till en 7-segments displaydrivrutin, till exempel GreenPAK-lösningen som beskrivs i Reference eller till en vanlig 74LS47 IC.

Kretsen som presenteras letar efter maximal spänning. För att konvertera konstruktionen till en minimispänningssökare måste en enkel förkonditioneringskrets läggas till mellan den analoga multiplexorn och GreenPAK-analoga ingången, och subtrahera multiplexerutgången från en 1 V referensspänning.

Steg 2: Funktionsprincip

Designen syftar till att välja källa med maxspänning, därför utförs en skanning på hela arrayen medan det sista maxvärdet lagras och jämförs med nästa värde i ingången (som tillhör nästa spänningskälla i skanningen).

I det följande kommer vi att hänvisa till en komplett multiplexsekvens längs alla ingångar som en "scan" eller "loop".

Jämförelse mellan två värden uppnås inte med hjälp av ACMP -komponenter (finns dock i SLG46620G), utan snarare med DCMP -modulen, när värdena är digitaliserade respektive. Detta är en avancerad och förfinad teknik som först behandlades i Reference.

Figur 2 visar hur SLG46620G är uppbyggd för denna design.

Den analoga ingångssignalen går till ADC-ingången via PGA-komponenten med en inställd förstärkning på 1. Olika förstärkningsinställningar är också möjliga för att hitta den bästa matchningen med front-end-konditioneringselektroniken för att mappa ingångsspänningarna till 0-1 V utbud av GreenPAK ADC -modulen.

ADC: n fungerar i enkla lägen och omvandlar den analoga signalen till en 8-bitars digital kod, som sedan överförs till DCMP-modulen. Den digitala koden matas också in i SPI -blocket, konfigurerat som en ADC/FSM -buffert, där en digital kod kan lagras och inte ändras förrän nästa puls kommer till SPI CLK -ingången. Lägg märke till att ett dedikerat logikblock driver SPI CLK -ingången. Vi kommer att undersöka denna del senare, eftersom det här är "kärnlogiken" som är ansvarig för korrekt drift. En ny digital kod lagras endast i SPI -modulen om den tillhör den faktiska maxinspänningen.

DCMP -komponenten används för att jämföra nuvarande ADC -data med den sista vinnaren (det är det sista max som hittades) som lagras i SPI -blocket. Det kommer att generera en puls vid OUT+ -utgången när nya ADC -data är större än den föregående. Vi använder OUT+ -signalen för att uppdatera SPI -blocket med den nya vinnaren.

En global klocksignal driver ADC -omvandlingar och allmänna tidpunkter. När en konvertering har utförts pulserar ADC: s INT -utgångssignal, samordnad i tid med ADC: s parallella datautgång. Vi använder INT-utgången också för att öka en 3-bitars binär räknare, implementerad av DFF i Matrix1, vilket är användbart av tre skäl:

1. Räknarens utgångsledningar adresserar den externa analoga multiplexorn och betjänar således nästa ingångsspänning till ADC;

2. Räkningen fryses in i ett 3-bitars register (implementerat i Matrix1) för att lagra den tillfälliga vinnaren under en skanning;

3. Räkningen avkodas för att uppdatera ett andra 3-bitarsregister (implementerat i Matrix0) när en skanning är klar.

Steg 3: Logisk implementering

ADC -modulen tillhandahåller sekventiellt konverterade data för alla ingångsspänningar, en efter en, på obestämd tid. När multiplexern är adresserad 0b111 (decimal 7) rullar räknaren till 0b000 (decimal 0) och startar därmed en ny avsökning av ingångsspänningarna.

Under skanningen genereras ADC INT -utsignalen när parallelldatautmatningen är giltig. När denna signal pulserar måste den analoga multiplexorn växla till nästa ingång och förse PGA med motsvarande spänning. Därför är ADC INT-utgången den direkta klocksignalen från 3-bitars binärräknaren i figur 2, vars 3-bitars parallella utgångsord direkt adresserar den externa analoga multiplexorn ("V select" i figur 1).

Låt oss nu hänvisa till ett exempel där ingångsspänningarna ska ha följande samband:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

Figur 3 representerar huvudsignalerna som är involverade i max-beslutsmekanismen.

Eftersom data så småningom klockas in i SPI -buffertregistret synkront med INT -pulser finns det ett jämförelsefönster där SPI -buffertinnehållet jämförs med nästa ADC -konverteringsresultat. Denna speciella timing resulterar i generering av OUT+ -pulser vid DCMP -utgången. Vi kan dra nytta av dessa pulser för att ladda nya värden i SPI -buffertregistret.

Såsom framgår av SPI -buffertdatalinjen i föregående bild innehåller SPI -registret alltid, det gångna gång, det största värdet bland de 8 ingångarna och det uppdateras endast när ett större värde detekteras av DCMP -modulen (med hänvisning till DCMP OUT+ utgångslinje för diagrammet, de saknade pulserna gör att V2 förblir låst i registret tills det jämförs med V5).

Steg 4: Lösa dödläge

Om den implementerade logiken skulle vara precis som beskrivs ovan är det klart att vi skulle stöta på en dödläge: systemet kan endast detektera spänningar högre än den som motsvarar det som lagras i SPI -buffertregistret.

Detta är också giltigt om denna spänning skulle minska och sedan en annan ingång, tills nu lägre än så, blir den högsta: den skulle aldrig detekteras. Denna situation förklaras bättre i figur 4 där endast 3 ingångsspänningar är närvarande för att klarhet.

Vid tidpunkten för iteration 2 sjunker V3 och V1 är den faktiska maxspänningen. Men DCMP -modulen ger inte en puls eftersom data som lagras i SPI -buffertregistret (motsvarande 0,6 V) är större än det som motsvarar V1 (0,4 V).

Systemet beter sig då som en "absolut" maxfinder och uppdaterar inte utmatningen korrekt.

Ett bra sätt att övervinna detta problem är att tvinga om att ladda om data till SPI -buffertregistret när systemet har slutfört en fullständig avfrågningscykel för alla kanaler.

Faktum är att om spänningen vid den ingången fortfarande är den högsta, ändras ingenting och kontrollen fortsätter säkert (med hänvisning till figur 4 ovan, så är det fallet med Loop Iterations 0 och 1). Å andra sidan, om spänningen vid den ingången av en slump minskar till ett värde mindre än en annan ingång, ger omladdning av värdet möjlighet för DCMP -modulen att producera en OUT+ -puls när den jämförs med det nya maxvärdet (detta är fallet med Loop Iterations 2 och 3).

En bit logikkrets är nödvändig för att övervinna problemet. Den måste generera en klocksignal till SPI-komponenten när slingan når den faktiska maxingången, och tvingar således en omladdning av dess uppdaterade dataord till SPI-buffertregistret. Detta kommer att diskuteras i avsnitt 7.2 och 7.6 nedan.

Steg 5: Enhetskonfiguration - Matrix0 -krets

SLG46620G har två Matrix -block, som visas i figur 2. Följande figurer visar respektive enhetskonfigurationer.

Den övre delen av kretsen är "Loop Register" realiserad med 3 DFF: er (DFF0, DFF1 och DFF2). Det uppdateras efter varje slinga i ingångsmultiplexern för att skicka binärnumret för "vinnaren" till en 7-segmentdisplaydriver, det vill säga ingången med högsta spänning i den senaste skanningen. Både klockan till DFF: erna och data kommer från logiken som implementeras i Matrix1 via port P12, P13, P14 och P15.

Den nedre delen är den analoga fronten med ingång på Pin 8 och PGA med förstärkning x1. ADC INT -utgången går både till SPI: s klocklogik och till Matrix1 via port P0, där den kommer att fungera som klocksignal för den implementerade räknaren.

ADC- och SPI -parallella datautgångar är märkta NET11 respektive NET15 för att anslutas till DCMP -komponenten i Matrix1.

Steg 6: Enhetskonfiguration - SPI Clocking Logic

Som påpekats tidigare i avsnittet "Logisk implementering" uppdateras SPI -buffertregistret varje gång en jämförelse mellan det verkliga lagrade värdet och de nya ADC -konverteringsdata genererar en puls vid DCMP OUT+ -utgången.

Signalintegritet säkerställs om denna signal är OCH-ed med ADC INT-utgången. Detta undviker spik och falsk utlösning.

Vi har också understrykt att SPI -bufferten måste uppdateras när slingan når den faktiska vinnardata för att hoppa över dödläge.

Tre signaler finns sedan i spelet för korrekt SPI -klockning:

1. ADC INT-utgång (LUT0-IN1)

2. DCMP OUT+ utgång (LUT0-IN0 via port P10)

3. Räkningen är lika med låssignal (LUT0-IN2 via port P11)

De två första är AND-ed och båda OR-ed med de senare i LUT0, vars implementering är konfigurerad som i figur 6.

Steg 7: Enhetskonfiguration - Egenskaper för Matrix0 -komponenter

Figurerna 7-10 visar de återstående komponentegenskapsfönstren som tillhör Matrix0.

Steg 8: Enhetskonfiguration - Matrix1 -krets

Steg 9: Enhetskonfiguration - 3 -bitars binär räknare

Den övre delen av kretsen innehåller logiska element, huvudsakligen en 3-bitars binär räknare klockad av ADC INT-utgången, som redan diskuterats. Denna räknare är implementerad med en ganska "standard" schemat som visas i figur 12.

Denna räknare realiseras i vår design med hjälp av flip-flops DFF9, DFF10, DFF11 och INV1, LUT4, LUT8. DFF9 -utgången är LSB medan DFF11 är MSB enligt figur 13.

LUT4 konfigureras som en XOR medan LUT8 utför AND-XOR-logiken i figur 12.

Räkneutgångar går till tre digitala utgångsstiften för att adressera den externa analoga multiplexern.

LUT10 avkodar räknarens kod när en skanning är klar och matar en puls till Matrix0 via DLY8 och port P12. Detta uppnås helt enkelt genom att AND-inga räknarens utgångar, och därmed avkoda nummer 7 dec (0b111 binärt, slutet av slingan).

Steg 10: Enhetskonfiguration - 3 -bitars jämförelselogik

Figur 15 visar kretsen som används för att detektera när slingan itererar vid den aktuella "vinnar" -adressen. I det här fallet, som redan diskuterats, bör en digital puls tvinga en omladdning av det aktuella ADC-resultatet för att lösa en möjlig dödläge.

"Vinnar" -adressen lagras i det temporära registret för Matrix1 (se nedan), medan den aktuella adressen matas ut av den binära räknaren.

XNOR -grindar ger en sann (logisk 1 eller "hög") utgång när båda ingångarna är lika. OCH-ing denna signal för alla bitar (LUT9) ger oss en puls när båda binära koder är desamma. Detaljer om XOR -grindar som paritetskontroll finns i Referens.

Signalen "Counter-equals-Latch" skickas till Matrix0 via port P11.

Steg 11: Enhetskonfiguration - Digital jämför logik och tillfälligt register

Den nedre delen av figur 11 (markerad i figur 16) visar DCMP-blocket, den beslutande delen av denna design.

DFF6, 7 och 8 bildar ett 3-bitars register för att lagra det tillfälliga inmatningsnumret "vinnare" medan slingan är igång. Inmatning till flip-flops är 3-bitars binära räknare, som syns i den globala Matrix1-kretsen i figur 11, som hoppas över för tydlighetens skull.

Utdata från detta register kan inte direkt styra den 7-segmentiga displayen eftersom värdet som lagras här ändras under en skanning och bör betraktas som "giltigt" först i slutet av själva skanningen.

Av denna anledning ansluter de tillfälliga registerutgångarna till Matrix0: s loopregister via intermatrisportarna P13, P14 och P15.

Det är viktigt att observera i figur 16 att det temporära registret klockas av DCMP OUT+ -utgången när ADC-SPI-registreringsjämförelsen resulterar i ett nytt max-värde.

Samma OUT+ -signal skickas till Matrix0, SPI CLK Logic, via port P10.

Steg 12: Enhetskonfiguration - Egenskaper för Matrix1 -komponenter

Figurerna 17-19 visar komponentegenskapsfönstren som tillhör Matrix1.

Steg 13: Resultat

För att testa implementeringen har en utvärderingskortprototyp konstruerats där de 8 analoga ingångsspänningarna erhålls med en serie motståndsdelare med TrimPots (som visas i figur 20).

Multiplexern som används är en ADG508, en del som kan fungera med en enda matning (12 V).

Den 7-segmentiga skärmdrivrutinen är en 74LS47. Det avkodar ett parallellt ingångsord och driver direkt en gemensam-anods 7-segmentskärm.

Utvärderingskortet har en 2x10 rätvinklig kontakt för att anslutas direkt till en GreenPAK Advanced Development Platform vid dess expansionskontakt som visas i figur 21.

Kombinationen med GreenPAK Advanced Development Platform gör det mycket enkelt att göra mätningar av signalerna för en snabb kontroll. Till exempel visar figur 22 en uppsättning signaler (respektive CLOCK, ADC INT -utgång och DCMP OUT+ -utgång) som fångats av en HP 54620A Logic Analyzer. Vågformer utlöses av en stigande kant av OUT+ -signalen (på omfånget märkt som 'A> B'), därför är detta en vågformsavläsning när en ny maxspänning detekteras bland de analoga ingångarna. Faktum är att den erhölls genom att rotera en av TrimPots på utvärderingskortet för att öka motsvarande spänning som visas i figur 22.

Figur 23 visar schemat över utvärderingsnämnden.

Slutsats

I denna instruktionsbok implementerade vi en åtta-kanalig max (eller min) spänningssökare som ska användas som ett vanligt tillägg till flerkanaliga styrsystem. Den presenterade metoden utnyttjar avancerade funktioner i GreenPAK -komponenterna och visar hur det är möjligt att integrera i ett enda chip analoga och digitala funktioner. Flera kommersiella IC: er kan ersättas med Dialog GreenPAK så att applikationsstorleken och kostnaden kan reduceras.

Rekommenderad:

Hur gjorde jag min egen boxningsmaskin ?: 11 steg (med bilder)

Hur gjorde jag min egen boxningsmaskin ?: Det finns ingen fantastisk historia bakom det här projektet - jag har alltid alltid gillat boxningsmaskinerna som fanns på olika populära platser. Jag bestämde mig för att bygga min

Min DIY Peltier Cooler! - DEKOMMISSIONERAD: 9 steg (med bilder)

Min DIY Peltier Cooler! - DEKOMMISSIONERAD: Jag ville alltid ha ett sätt att hålla matvarorna tillräckligt svala i min bil utan att behöva rusa hem till mitt kylskåp. Jag bestämde mig för att använda en gammal Peltier värmeväxlare som jag gjorde för några år sedan. Jag klämde in Peltier mellan två kylflänsar i aluminium. Stora

Spänningsmonitor för högspänningsbatterier: 3 steg (med bilder)

Spänningsmonitor för högspänningsbatterier: I den här guiden kommer jag att förklara för dig hur jag byggde min batterispänningsmonitor för min elektriska longboard. Montera den hur du vill och anslut bara två ledningar till ditt batteri (Gnd och Vcc). Denna guide antog att din batterispänning överstiger 30 volt,

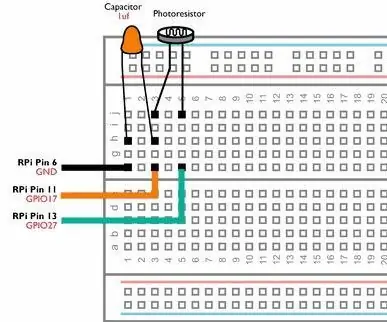

Raspberry Pi GPIO -kretsar: Användning av en LDR -analog sensor utan ADC (analog till digital omvandlare): 4 steg

Raspberry Pi GPIO -kretsar: Användning av en LDR -analog sensor utan ADC (analog till digital omvandlare): I våra tidigare instruktioner har vi visat dig hur du kan koppla din Raspberry Pi: s GPIO -stift till lysdioder och switchar och hur GPIO -stiften kan vara höga eller låg. Men vad händer om du vill använda din Raspberry Pi med en analog sensor? Om vi vill använda en

Picaxe -baserad digital termometer med max och min: 13 steg

Picaxe-baserad digital termometer med max och min: (Lämna ett meddelande, men var inte för kritisk, det här är min första instruerbara !!) Detta är en termometer jag gjorde för vår husbil, för att visa yttemperaturen. Det är baserat på ett Picaxe -chip eftersom de är billiga och enkla att använda. Om detta är för