Innehållsförteckning:

- Författare John Day day@howwhatproduce.com.

- Public 2024-01-30 12:44.

- Senast ändrad 2025-01-23 15:11.

Har du någonsin föreställt dig hur ditt tangentbord tar in och hur data lagras! Detta projekt är en mindre version av datainmatning och lagring. En detaljerad förklaring till hur signalen från knapparna, klockan påverkar minneselementen (flip -flops).

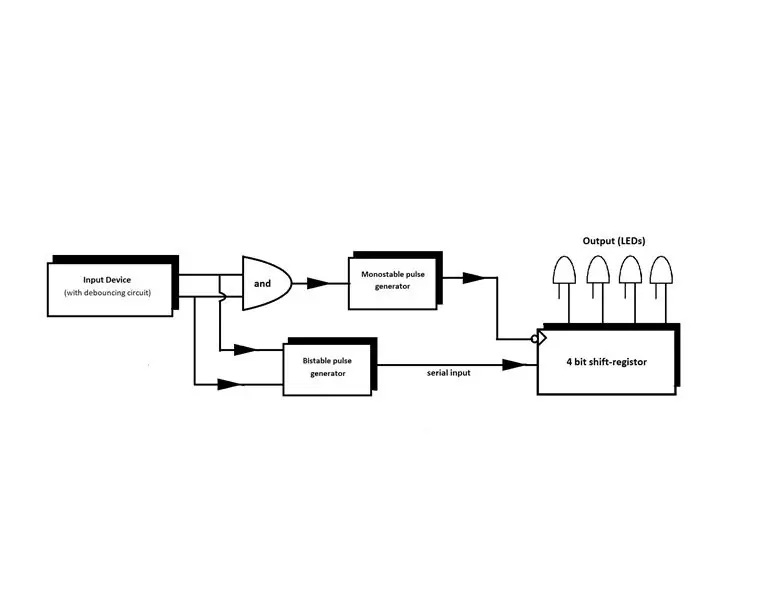

Steg 1: Block Diagram

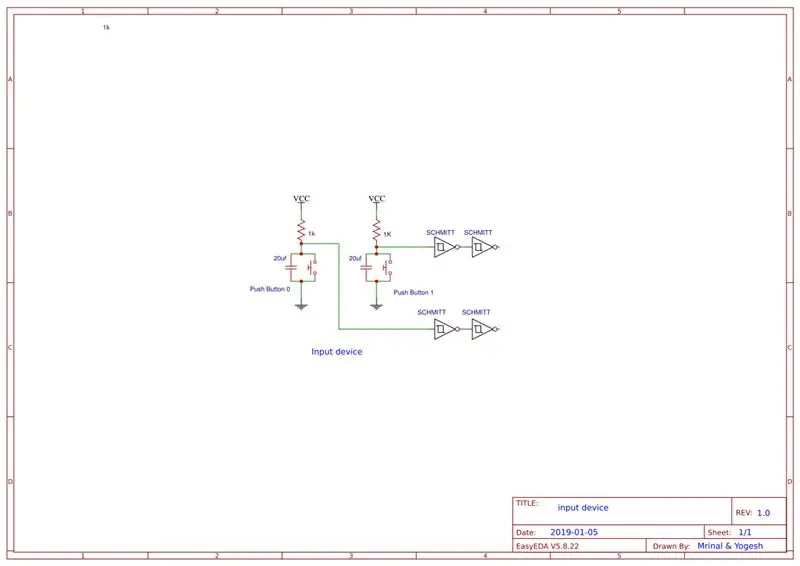

1. Mata in enhet

Asa binär 4 -bitars ingångsenhet finns det bara två tryckknappar (en för att registrera 1 (hög) och en annan för 0 (låg) med ett brusfilter som krävs för att generera insignalen. Utsignalen som genereras är en nollpuls (när knappen trycks in ändras alltid den höga signalen till låg).

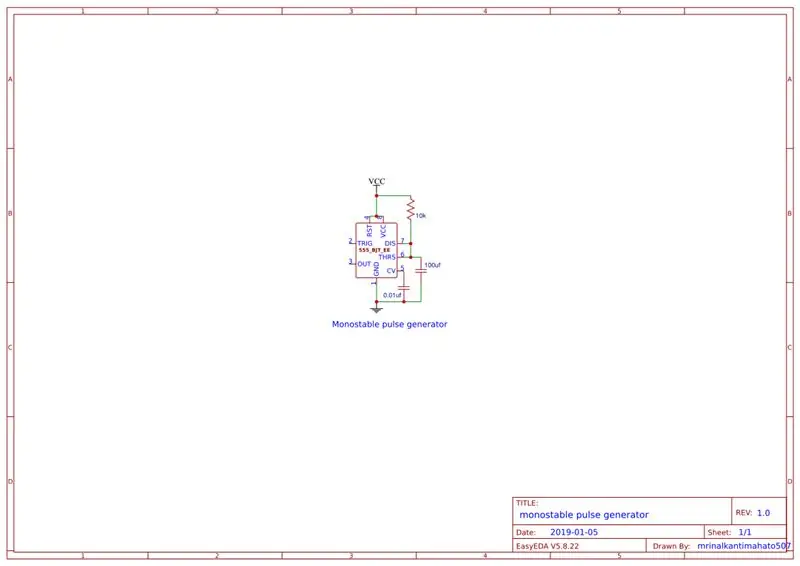

2. Monostabil pulsgenerator

Ingångssignalerna matas sedan in i den monostabila pulsgeneratorn för att generera en puls som har en fast högtidstid, den triggas av den lilla ingångspulsen. Denna monostabila puls används som en klockingång till skiftregistret.

3. Bi-stabil pulsgenerator

Denna puls drivs också av ingångssignallinjerna, när den ena (höga) knappen trycks in ställs denna signal in och återställs när den låga knappen trycks ned. Signalen matas som den vänstra seriella ingången till skiftregistret.

4. Skiftregister

4-bitars skiftregistret använder 4 flip-flops för att lagra data. Det krävs en seriell ingång med en klocka för att lagra data antingen från vänster till höger eller höger till vänster. I detta projekt kommer de seriella data som vi använder från den Bi-stabila pulsgeneratorn och klocksignalen från en monostabil pulsgenerator.

5. Utgång

Lysdioderna indikerar utgången.

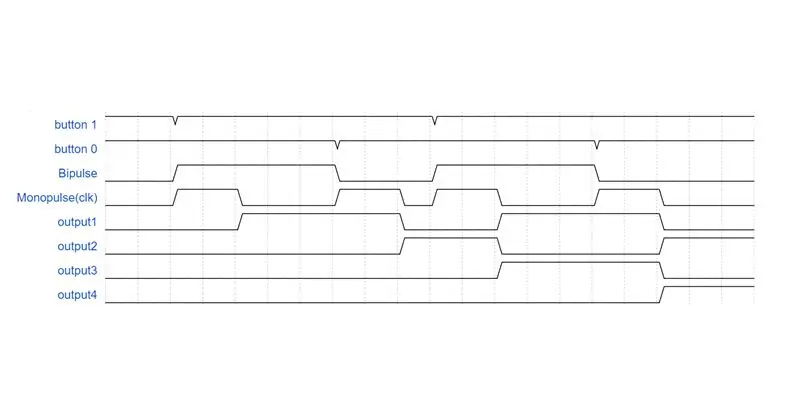

Steg 2: Tidsdiagram

Ett provtagningsschema som tar en ingång 0101. Ingångspulsen från knapp 1 och knapp 2 har en mycket liten "låg tid", det är anledningen till att den visas som en spik i tidsdiagrammet.

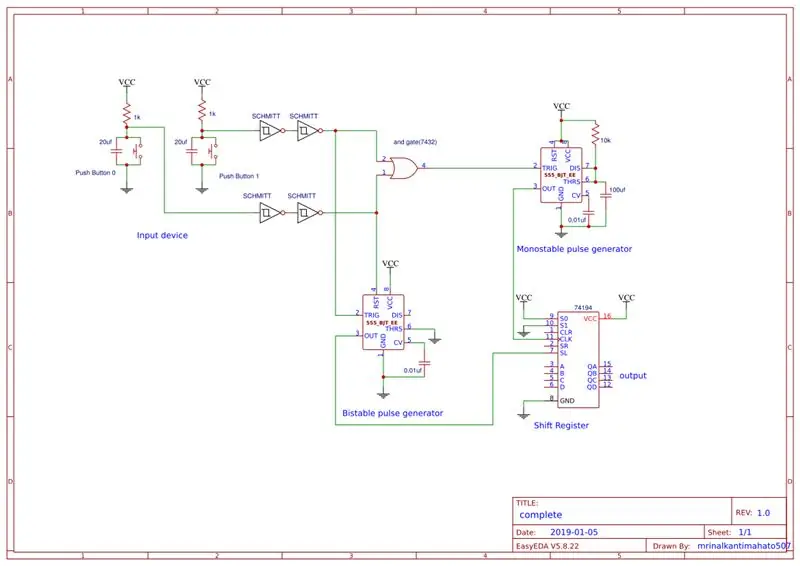

Steg 3: Kretsdiagram

Högtiden för den monostabila pulsen kan ändras genom att ändra RC -värdet (motstånd och kapacitansvärde). Hög tid anges med t = 1,1*RC. Högtiden har en nedre gräns som beror på denonceringsomkopplaren som används, gränsen är i allmänhet 10-20ms. Den höga tiden i denna kretsdesign är 1s (10k omh*100uf).

Detta genom att minska den här tiden ökas enhetens hastighet.

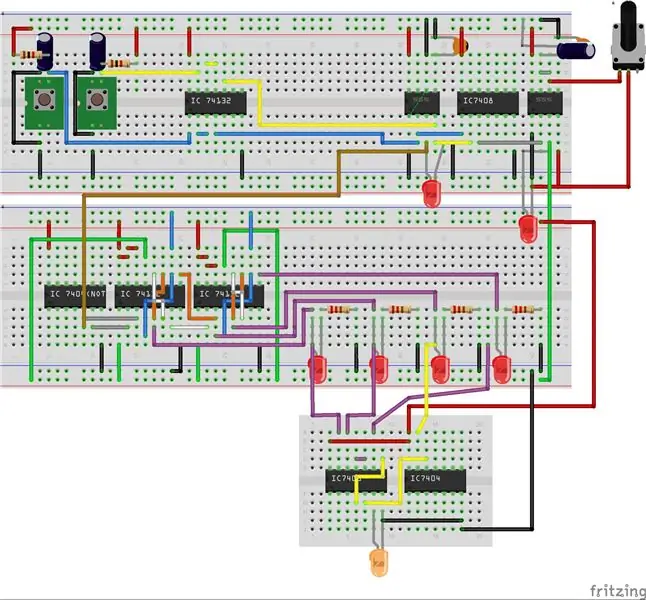

Steg 4: Fritzing -design med BOM -filer

Ladda ner fritzing -filen för att anpassa designen och skapa din egen design.

Den obligatoriska komponentlistan finns i BOM -filen.

Rekommenderad:

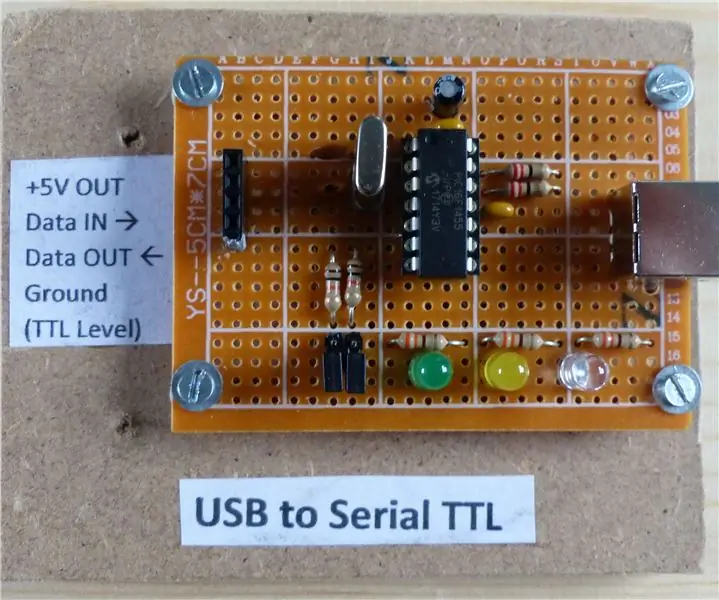

USB till seriell TTL: 3 steg

USB till seriell TTL: För några av mina PIC -projekt behöver jag ett seriellt (RS232) gränssnitt för att skriva ut några meddelanden på datorns skärm. Jag har fortfarande en stationär dator som har ett RS232 -gränssnitt men numera har de flesta datorer ett USB -gränssnitt istället. Du kan köpa dev

OrangeBOX: OrangePI -baserad säker lagringsenhet för säkerhetskopiering: 5 steg

OrangeBOX: OrangePI-baserad säker lagringsenhet: OrangeBOX är en allt-i-ett fjärrlagringsbackup för alla servrar. Din server kan vara infekterad, skadad, torkad och alla dina data är fortfarande säkra på OrangeBOX och vem skulle inte vilja ha ett omöjligt uppdrag som backup -enhet vad du bara planerar

Hur man formaterar om en extern lagringsenhet med Mac OS X: 10 steg

Hur formaterar jag om en extern lagringsenhet med Mac OS X: säljer en gammal USB? Eller dator? Använd den här enkla steg-för-steg-guiden för att formatera om din externa lagringsenhet på din Mac. Fördelarna med att omformatera en hårddisk är delsäkerhet, dels bekvämlighet och dels återanvändbarhet. Detta hjälper till att

Passiv 3 -ingångs stereomixer: 4 steg

Passiv 3 -ingångs stereomixer: Denna instruerbara visar dig hur du bygger en enkel stereomixer. Även om denna låda bara har 3 stereoingångar kan du enkelt uppgradera den till så många du behöver! Jag ville bygga den här rutan för att ansluta flera ljudingångar till en enda utgång. Jag är

USB Hub -lagringsenhet i disketter !: 5 steg

USB Hub -lagringsenhet i disketter !: Vill du alla ha en portalagringsenhet som är väldigt lätt, har minst 8 GB lagringsutrymme, du behöver inte bry dig om den ramlar ner, du kan ha den överallt och du kan bära faktiskt alla operativsystem med vissa Office -program och alla dessa applikationer