Innehållsförteckning:

- Författare John Day day@howwhatproduce.com.

- Public 2024-01-30 12:40.

- Senast ändrad 2025-01-23 15:10.

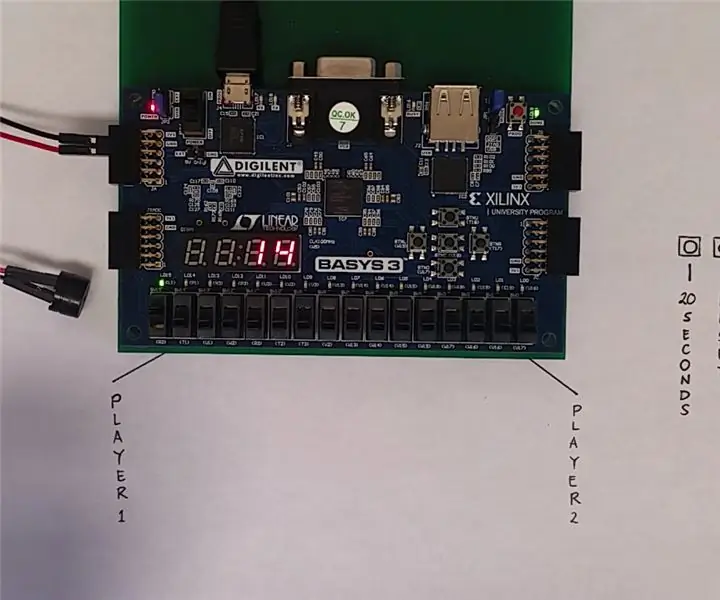

Det konkurrenskraftiga summer -systemet som utformats i detta projekt fungerar på samma sätt som de summer -system som används i Regional och National Science Bowl -tävlingar. Det här projektet inspirerades av mitt engagemang i mitt gymnasieskolor i tre år. Vi har alltid haft en önskan att återskapa lock-out summer systemet med en 5-sekunders och 20-sekunders timer.

För att ge lite bakgrund om summer -systemet är science bowl -summerna programmerade att mata in högst 8 spelare (med 8 separata summer). När en summer har tryckts på tänds den första personens summer för att indikera vilken spelare som får frågan. Resten av spelarna kommer att "låsas ute" vilket innebär att deras summer inte svarar förrän moderatorn återställer summern.

När moderatorn har läst frågorna trycker han på en knapp för att starta nedräkningstimern som kommer att visas på displayen med sju segment. Efter en "toss-up" fråga kan moderatorn trycka på höger knapp för att starta nedräkningen från 5 sekunder. Under tiden, efter en "bonus" -fråga, kan moderatorn trycka på vänster knapp för att starta nedräkningen från 20 sekunder. När timern når noll indikerar en ljudsummer att spelaren har tagit slut.

För att återställa systemet och nedräkningstimern kan moderatorn trycka på mittknappen. För att återställa låsmekanismen och lysdioderna för spelare måste omkopplarna för spelare 1 och spelare 2 vara låga.

Steg 1: Material

Du behöver följande:

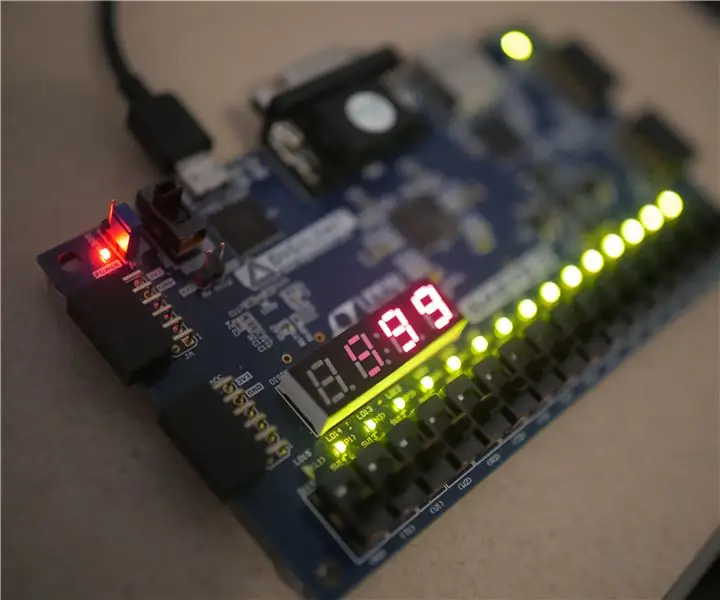

- Basys3 -kort (eller motsvarande FPGA -kort)

- Micro-B USB-kabel

- Högtalare (jag använde en passiv högtalare)

- 2 trådar

- Programvara för att implementera på FPGA (jag använde Vivado)

- Konkurrenskraftig summer -fil

Steg 2: Black Box Diagram

Den svarta rutan visar de ingångar och utgångar som kommer att användas i detta summer -system.

INGÅNG:

player1, player2 Dessa ingångar är anslutna till två switchar på Basys3 -kortet. För enkelhets skull kommer omkopplarna längst till vänster och längst till höger att användas.

Återställ Mittknappen används för att representera återställningsknappen.

count_down_20_sec Den vänstra knappen används för att representera 20-sekunders timer-knappen.

count_down_5_sec Den högra knappen kommer att användas för att representera 20-sekunders timer-knappen. För att säkerställa att både 20-sekunders- och 5-sekunders-timern startar, håll knappen intryckt tills displayen i sju segment visar timern.

CLK FPGA -kortet kommer att generera en klocka som går med en frekvens på 10 ns.

UTGÅNG:

högtalare Högtalarutgången är ansluten till en extern summer eller högtalare. Du måste ansluta högtalaren till Basys3 -kortets JA pmod -portar. Detta steg kommer att beskrivas nedan.

speaker_LED Denna utgång är ansluten till en lysdiod i mitten av kortet och kommer bara att indikera när högtalarutgången på FPGA är hög. Du kan använda detta för att testa din externa högtalare. Observera att några av pmod -portarna kanske inte fungerar som de ska, så du kan prova olika och använda LED: n för att kontrollera om högtalaren ska vara på.

SEGMENT Denna utmatning är ansluten till de åtta enskilda segmenten på sjusegmentsdisplayen, inklusive decimalpunkten.

DISP_EN Denna utgång är ansluten till de fyra anoderna på displayen med sju segment.

player_LED Denna utgång är en 2-buntssignal som är ansluten till lysdioderna ovanför switch1- och player2-switcharna. Den första spelaren som vänder motsvarande omkopplare indikeras av lysdioden. Observera att båda lysdioderna inte kan tändas samtidigt.

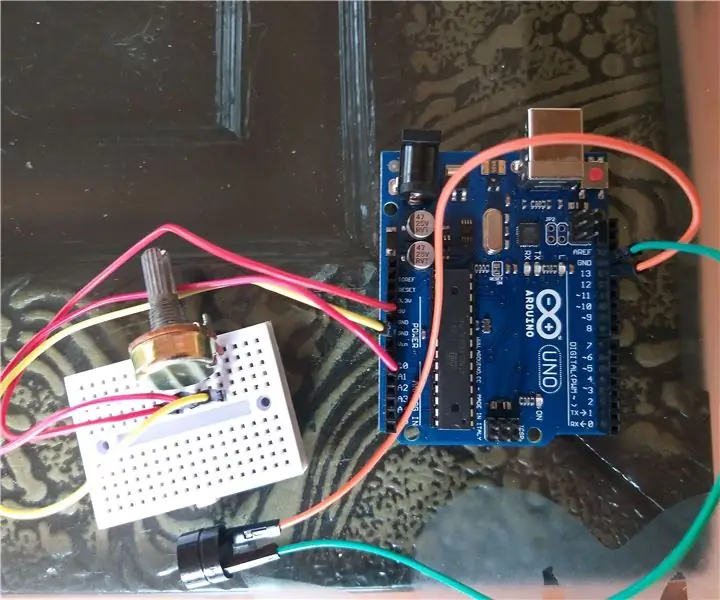

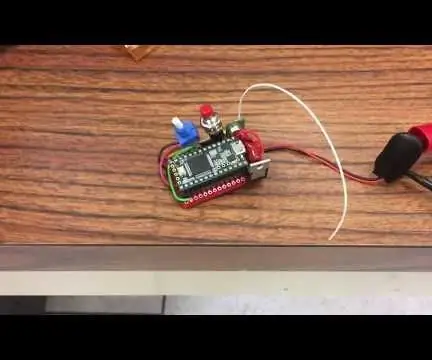

Steg 3: Anslutning av den externa högtalaren

För att ansluta den externa högtalaren till Basys3 -kortet, ta dina två ledningar och fäst dem enligt bilden ovan. Den vita linjen ansluter högtalarens negativa terminal till jordporten på kortet. Den röda linjen ansluter högtalarens positiva terminal till JA10 pmod -porten på kortet.

Begränsningsfilen är utformad så att alla portar från JA1 till JA10 ska fungera. Vissa stift på brädet svarar dock inte, så om JA10 inte fungerar kan du prova de andra portarna.

Steg 4: Strukturdiagram

Bilden ovan visar strukturdiagrammet för det konkurrenskraftiga summersystemet inklusive alla komponenter som utgör huvudmodulen. Deras beskrivningar är följande:

player_lockout_LED1 Spelarens lockout-LED-komponent är en slutmaskin som använder en-het-kodning. Den har fyra ingångar: player1, player2, reset och CLK. Den innehåller en 2-bitars buntutgångsspelare_LED. Ingångarna och utgångarna för player_lockout_LED1-komponenten är alla direkt anslutna till de identiskt namngivna ingångarna och utgångarna på huvudmodulen.

buzzer_tone1 Summerkomponenten är baserad på den här koden som publiceras på ett forum

stackoverflow.com/questions/22767256/vhdl-… Det modifierades dock för att mata ut ett kontinuerligt ljud med en frekvens av 440 Hz (en notering). Aktiveringsingången är ansluten till en summer summerbar som är en utsignal från komponenten down_counter_FSM1.

clk_div1 Klockavdelningskomponenten är en modifierad version av professor Bryan Mealys klockavdelare som finns på PolyLearn. Det saktar ner klockan så att utgångsperioden är 1 sekund.

down_counter_FSM1 Nedräknaren är en FSM som är utformad för att räkna ner till noll. De två möjliga starttiderna är 20 eller 5 som väljs av användarinmatningen. Den matar ut '1' när timern har nått noll för att indikera att tiden har tagit slut. Denna utgång fungerar som en aktivering för summertonskomponenten. Räknaren matar också ut en 8-bitars buntsignal som skickar en 8-bitars BCD som skickas till segmentavkodaren. En annan utgång är counter_on som också är ansluten till den giltiga ingången på segmentavkodaren.

sseg_dec1 Avkodarkomponenten med sju segment finns på PolyLearn och är skriven av professor Bryan Mealy. Den använder en BCD-ingång från down_counter_FSM1 och matar ut decimalekvivalenten på sjusegmentsdisplayen. När räknaren är på är den giltiga ingången hög. Detta gör att avkodaren kan visa decimaltalet på sjusegmentsdisplayen. När räknaren är avstängd är den giltiga ingången låg. Displayen med sju segment visar då bara fyra streck.

Steg 5: Finite State Machine (FSM) -diagram

Känslighetslistan för finite state -maskinen innehåller player1, player2, reset och klockan. FSM-utgången är en 2-bitars bunt player_LED ansluten till två lysdioder på Basys3-kortet. Den slutliga tillståndsmaskinen visar följande tre tillstånd:

ST0 är startläget. I detta läge är de två lysdioderna släckta. FSM förblir i detta tillstånd om både spelare1 och spelare2 är låga. En asynkron återställning sätter också tillståndet till ST0. När player1 -omkopplaren är inställd på hög blir nästa tillstånd ST1. Om player2 -omkopplaren är inställd på hög blir nästa tillstånd ST2.

ST1 är det tillstånd för vilket spelare 1 lyser. FSM förblir i detta tillstånd för alla ingångar. Detta innebär att även när player2 -omkopplaren är inställd på hög omedelbart efter att player1 -omkopplaren är hög, kommer den att förbli i ST1. Endast asynkron återställning kan ställa in nästa tillstånd till ST0.

ST2 är det tillstånd för vilket player2 LED är tänd. I likhet med ST !, kommer FSM att förbli i detta tillstånd för alla ingångar, även när player1 -omkopplaren är inställd på hög direkt efter att player2 -omkopplaren är hög. Återigen kan bara asynkron återställning ställa in nästa tillstånd till ST0.

Rekommenderad:

Summer Fan Cooling Baseball Cap: 6 steg

Summer Fan Cooling Baseball Cap: En dag när jag letade igenom min garderob såg jag en gammal röd basebollkeps som jag har köpt förra året. Plötsligt och en idé dök upp i mitt sinne, kunde jag ändra denna gamla keps till en cool produkt som heter fläktmössa, en mycket speciell innovationsprodukt

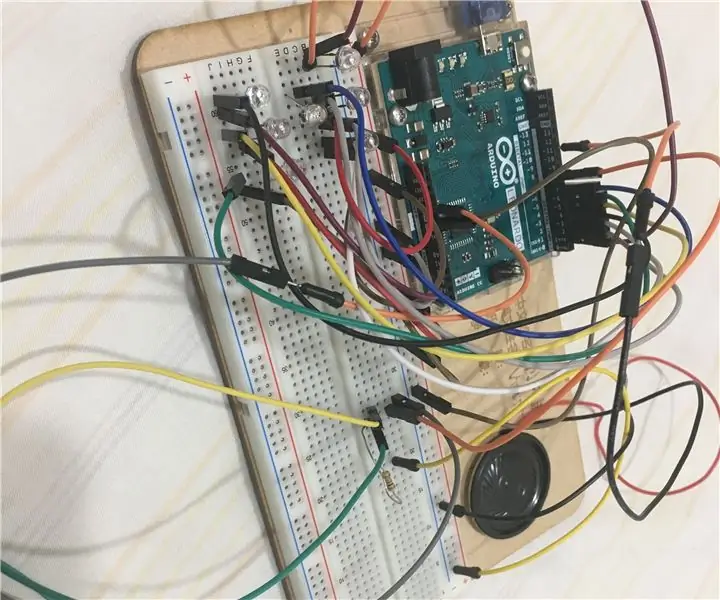

Super Mario med hjälp av summer: 3 steg

Super Mario Using Buzzer: Lyssnar på musik slappnar vårt sinne och själ. Låt oss lägga till lite musik till dina arduino -projekt med en enda komponent, summer.Jag hittade detta fantastiska projekt med Buzzer som spelar super mario temasång skriven av Dipto Pratyaksa på instruktörer. Dessutom

Fjärrstyrd summer för förlorade och hittade: 4 steg

Fjärrstyrd summer för borttappad och hittad: Denna tvådelade krets består av en summer och en styrenhet. Fäst summern på ett objekt som du ofta kan tappa och använd knappen och volymknappen på kontrollen för att aktivera summern när objektet försvinner. Summern och kontrollen

LED -tärningar med summer: 6 steg

LED-tärningar med summer: Denna instruktör lär dig hur man gör en LED-tärning med summer när knappen trycks in. Ursprunglig källa: https://www.instructables.com/id/Easy-Arduino-LED-Dice

2 -spelare konkurrenskraftigt VS -tidsspel: 4 steg

2 Player Competitive VS Timing Game: Du behöver: 1.Digilent Basys 3, FPGA Board (eller någon annan FPGA,) 2. En relativt aktuell version av Vivado, eller någon annan VHDL -miljö3. En dator som kan köra det nämnda programmet