Innehållsförteckning:

- Författare John Day day@howwhatproduce.com.

- Public 2024-01-30 12:37.

- Senast ändrad 2025-01-23 15:10.

I denna handledning kommer vi att använda FPGA för att styra extern LED -krets. Vi kommer att genomföra följande uppgifter

(A) Använd tryckknapparna på FPGA Cyclone IV DuePrologic för att styra LED.

(B) Flash -LED tänds och släcks regelbundet

Videodemo

Lab-meny: https://roywchpi.blogspot.com 2020/06/10-fpga-dueprologic-push-button-led.html

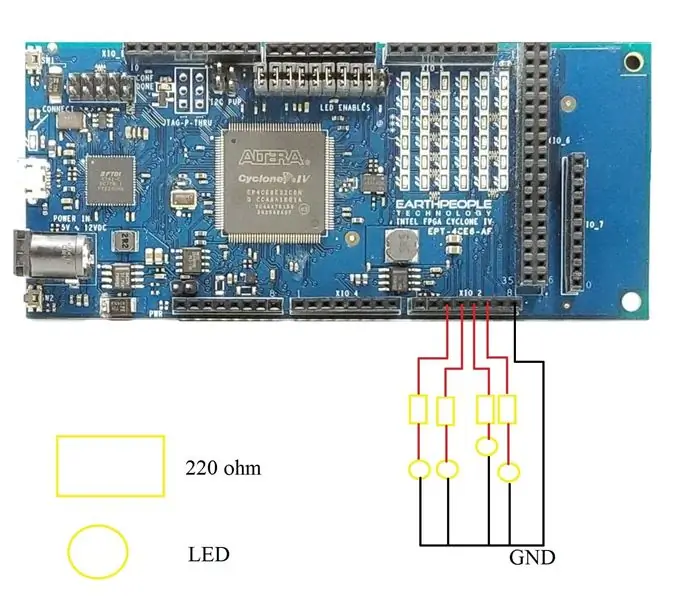

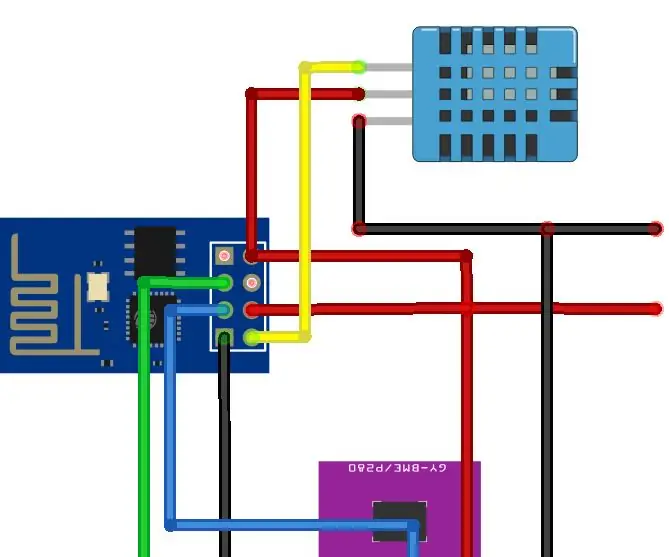

Steg 1: Bygg en elektronisk krets

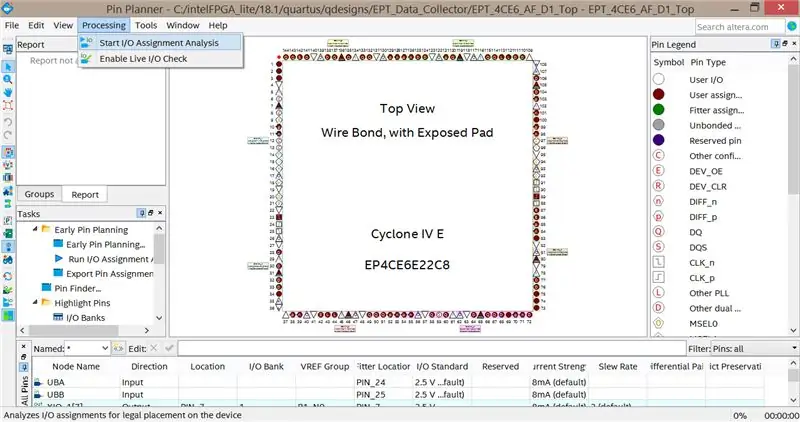

Steg 2: Kontrollera Pin -planeraren och redigera Verilog -koden

Steg 3: Redigera Verilog -kod

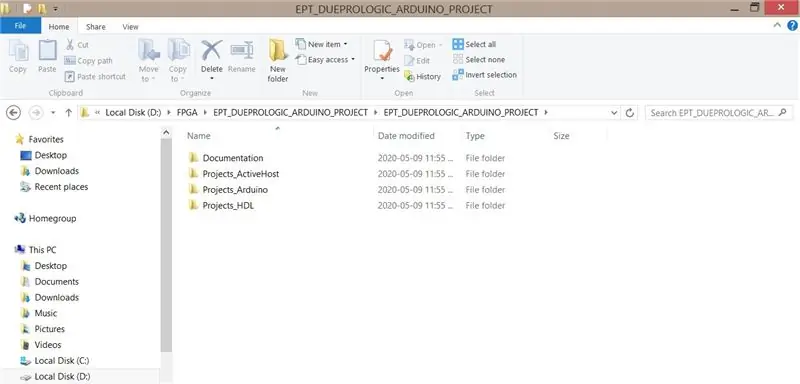

När du köper FPGA DueProLogic bör du få en DVD. När du har öppnat "Projects_HDL" bör du se den ursprungliga kodfilen

Lägg till den markerade koden. Det registrerar I/O -portarna och tilldelar nummer till portarna.

utmatningskabel [7: 0] XIO_1, // XIO-D2-D9

utgångskabel [5: 0] XIO_2, // XIO-D10-D12

utmatningskabel [5: 0] XIO_3, // XIO-D22-D29

ingångskabel [5: 0] XIO_4, // XIO-D30-D37

ingångskabel [5: 0] XIO_5, // XIO-D38-D45

utmatningskabel [4: 0] XIO_6_OUT, // XIO-D46-D53

ingångskabel [31: 5] XIO_6, // XIO-D46-D53

utgångskabel [2: 0] XIO_7, // XIO - D69, D70, D71, D74, D75, D76

ingångskabel UBA, // Tryckknappsbrytare

ingångskabel UBB // Tryckknappsbrytare

tilldela XIO_1 [3] = start_stop_cntrl;

tilldela XIO_2 [1] = start_blinky; // LED -blixt LED på och av

tilldela XIO_2 [2] = 1'b1; // utmatning HÖG

tilldela XIO_2 [3] = ~ UBA; // Tryckknapp A

tilldela XIO_2 [4] = UBB; // Tryckknapp B

tilldela c_enable = XIO_5 [2];

tilldela LEDExt = XIO_5 [5];

Sedan måste vi ställa in en fördröjningstimer. Kommentera den ursprungliga timerkoden och skriv en ny timerfunktion

//-----------------------------------------------

// LED blinkande start

//-----------------------------------------------

/*

alltid @(posedge CLK_66 eller negedge RST)

Börja

om (! RST)

start_blinky <= 1'b0;

annan

Börja

if (control_register [7: 4]> 0)

start_blinky <= 1'b1;

annan

start_blinky <= 1'b0;

slutet

slutet

*/

reg [31: 0] ex;

första början

ex <= 32'b0;

start_blinky <= 1'b0;

slutet

alltid @(posedge CLK_66)

Börja

ex <= ex + 1'b1;

om (ex> 100000000) // blinkar på/av ~ 1,6 sekunder, klocka 66MHz

Börja

start_blinky <=! start_blinky;

ex <= 32'b0;

slutet

slutet

//-----------------------------------------------

// LED -fördröjningstimerräknare

//-----------------------------------------------

/*

alltid @(posedge CLK_66 eller negedge RST)

Börja

om (! RST)

led_delay_counter <= TIMER_LOW_LIMIT;

annan

Börja

if (ange [SELECT_MODE])

led_delay_counter <= timer_value;

annars om (ange [WAIT_FOR_TIMER])

led_delay_counter <= led_delay_counter - 1'd1;

slutet

slutet*/

Steg 4: Kompilera Verilog -kod

Tryck på "Starta kompilering" i Quartus, inget felmeddelande ska genereras.

Om du får ett felmeddelande om flera stift. Gå till Uppdrag -> Enhet -> Enhets- och stiftalternativ -> Dubbelsidiga stift -> ändra värdet på lämplig stift till "Använd som vanlig I/O".

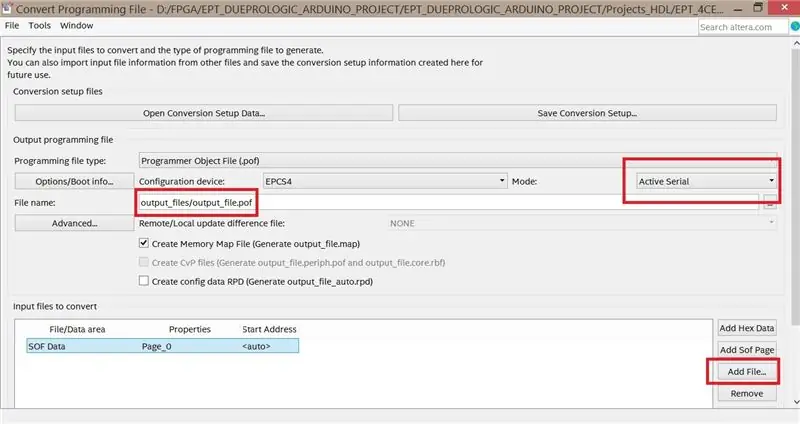

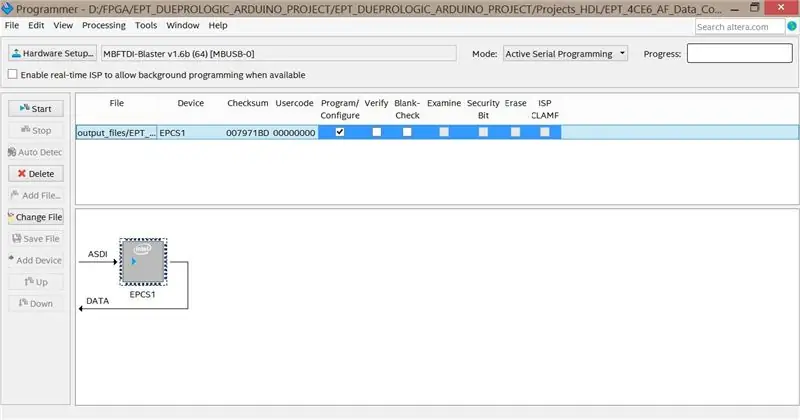

Efter sammanställningen bör du få pof -utmatningsfil direkt. Om din programvara inte är uppdaterad kan du bara få sof-fil. När det händer klickar du på "Arkiv" i Quartus -> "konvertera programmeringsfiler". Ändra inställningarna som är markerade med röda rutor.

Steg 5: Låt oss prova

Det borde ju fungera !!! Den gula lysdioden lyser alltid. Den röda lysdioden blinkar. Den blå lysdioden släcks om du trycker på knapp B. Den gröna lysdioden tänds om du trycker på knapp A

Rekommenderad:

FPGA Cyclone IV DueProLogic Controls Raspberry Pi -kamera: 5 steg

FPGA Cyclone IV DueProLogic Controls Raspberry Pi -kamera: Trots att FPGA DueProLogic är officiellt utformad för Arduino, kommer vi att göra FPGA och Raspberry Pi 4B överförbara. Tre uppgifter implementeras i denna handledning: (A) Tryck samtidigt på de två tryckknapparna på FPGA för att vända

FPGA Cyclone IV DueProLogic Controls Servomotor: 4 steg

FPGA Cyclone IV DueProLogic Controls Servomotor: I den här självstudien kommer vi att skriva Verilog -kod för att styra servomotorn. Servon SG-90 tillverkas av Waveshare. När du köper servomotorn kan du få ett datablad som visar driftsspänning, maximalt vridmoment och det föreslagna Pu

Arduino Cyclone Game: 5 steg (med bilder)

Arduino Cyclone Game: Jag har aldrig spelat det riktiga cyklonarkadespelet men jag gillar idén att spela med vår reaktionstid.Jag designade ett miniatyriserat spel. Den består av 32 lysdioder som bildar en cirkel, lysdioderna lyser upp en efter en som en ledjakt. Målet är att trycka på en rumpa

Arduino Cyclone Arcade Game: 6 steg

Arduino Cyclone Arcade Game: Blinkande flashiga lampor! Arduino! Spel! Vad mer behöver sägas? Detta spel är baserat på Cyclone -arkadspelet, där spelaren försöker stoppa en LED -rullning runt en cirkel på en viss plats

One More Arduino Weather Station (ESP-01 & BMP280 & DHT11 & OneWire): 4 steg

One More Arduino Weather Station (ESP-01 & BMP280 & DHT11 & OneWire): Här kan du hitta en iteration av att använda OneWire med de få få stiften på en ESP-01. val (du måste ha meriter …) Samlar in sensoriska data från en BMP280 och en DHT11