Innehållsförteckning:

- Författare John Day day@howwhatproduce.com.

- Public 2024-01-30 12:37.

- Senast ändrad 2025-01-23 15:10.

JDM är en populär PIC -programmerare eftersom den använder en serieport, ett minimum av komponenter och kräver ingen strömförsörjning. Men det finns förvirring där ute, med många programmeringsvarianter på nätet, vilka fungerar med vilka PIC? I denna "instruerbara" testar vi JDM och jag demonstrerar hur man simulerar kretsen med Spice som svarar på alla dina frågor!

Tillbehör

LTspice som kan laddas ner från Analog Devices här.

Du behöver också JDM -kretsfilerna här.

Steg 1: Krav på seriell port

JDM kräver en seriell port som uppfyller EIA232-specifikationen, helst med +12/-12 spänningsnivåer.

Enligt Texas Instruments Line Driver MC1488 datablad (Figur 3)

Utgångsimpedans = 4V/8mA = 500 ohm.

Kortslutningsströmgräns = 12mV, utan tidsbegränsning - ingen skada på chip.

Ingångsimpedans för linjemottagare = 3k till 7k ohm rekommenderas.

Seriella portar på äldre stationära datorer använder +12v/-12V som uppfyller detta krav.

Seriella portar på nyare bärbara datorer använder lägre spänningar. JDM kanske fungerar - svaret är mer komplext.

Steg 2: Krav på PIC -programmering

Information om PIC -programmeringskrav erhålls från Microchip. Ovanstående är för en typisk enhet.

Steg 3: JDM -specifikation

Har den ursprungliga JDM -webbplatsen gått förlorad i tidens dimmor? Detta gör att vi gissar vad designern ursprungligen avsåg för specifikationen.

- Ge VDD = 5V och upp till IDD = 2mA maximalt (för "in socket" -version)

- Ge VHH = 13V och upp till IHH = 0,2mA maximalt.

- MCLR Stigningstid tVHHR = 1uS max.

- ICSP-versionen måste kunna dra MCLR lågt mot 22k pull-up på målet.

Steg 4: Kretsbeskrivning

Figur JDM1 är baserad på den "vanliga" JDM -kretsen från PICPgm -webbplatsen. Detta är programmeraren "PIC in Socket" där PIC tar ström från TX- och RTS -stift. Det ursprungliga diagrammet var svårt att förstå så jag har ritat om det med hjälp av den normala konventionen för strömflöde uppifrån och ner. Och jag har lagt till LED -indikatorer "RESET", "PROG" och "RTS" som är nödvändiga under konstruktion och testning. Förhoppningsvis har dessa inga skadliga effekter på beteendet.

Den normala konventionen för kretsdesign är gemensam för alla grunder, men nyckelfunktionen för JDM är att seriell portjord (GND) är ansluten till VDD. Detta skapar förvirring när seriella portsignaler mäts med avseende på GND, PIC -signaler med avseende på logisk jord (VSS).

När TX går högt uppträder Q1 som två förspända dioder. (Q1 -kollektorn är inte omvänd förspänd som vid normal transistordrift). Q1 -kollektor laddar C2, som kläms fast vid VDD+8V av Zener (D3). Q1 -sändare levererar 13V till MCLR för program/verifieringsläge.

När TX blir låg laddas kondensatorn C3 via D1 och VSS kläms fast vid VDD-5V med zener (D5). TX är också fastspänt vid (VSS-0.6) med D1. Q1 är avstängd, C1 håller sin laddning för nästa programmeringspuls. MCLR kläms fast vid 0V med D2, så PIC är nu Återställ.

När RTS är hög sänds klockan till PGC. D4 klämma PGC vid VDD logik hög. När RTS är låg laddas kondensatorn C3 via D6 och VSS kläms fast vid VDD-5V med zener (D5). D6 klämmer PGC vid VSS eller logik 0.

Under programmeringen läses data som skickas ut på DTR på PGD, som PIC konfigurerar som ingång. När DTR är hög fungerar Q2 som "emitterföljare" och PGD-spänningen är ungefär (VDD-0.6) eller logisk 1. När DTR är låg fungerar Q2 som en dålig transistor (sändare och kollektorstift är omvända). Q2 drar PGD lågt, vilket kläms fast av D7 vid VSS eller logik 0.

Under verifiering konfigurerar PIC PGD som en utgång för att skicka data till serieporten. DTR måste vara högt och data läses på CTS. När PGD -utgången är hög är Q2 avstängd, CTS = DTR = +12V. När PGD -utgången är låg är Q2 på. Q2 -kollektorn drar ström (12V+5V)/(1k+1k5) = 7mA från DTR och drar CTS lågt till VSS.

Steg 5: Förbered dig för simulering

Ladda ner LT -krydda, spara och öppna kretsfilerna (*.asc) som tillhandahålls här. För att simulera kretsen måste vi ge den några ingångar och sedan "spåra" utgångarna. V1, V2 V3 simulerar 12V seriell port med utgångsimpedans R11, R12, R13.

- V1 genererar 2 programpulser på TX från 0,5 ms till 4,5 ms

- V2 genererar burst av datapulser på DTR från 1,5 till 4,5 ms

- V3 genererar burst av klockpulser på RTS från 0,5 till 3,5 ms

Komponenterna V4, X1, R15 och R16 är alla en del av simuleringen.

- V4 genererar 2 pulser från 2,5 till 4,5 ms för verifieringsdata.

- Bygel X1 simulerar OUTPUT på PGD.

- R15, R16 simulerar "laddning" av PIC på VDD och MCLR.

Steg 6: Ändringar för ICSP

Figur JDM3 visar versionen för "in circuit" -programmering. Ändringar från original är

- Byt ut ZIF -uttaget mot ICSP -kontakt.

- PIC -enheten drivs nu av matning till målkretsen (V5).

- Ta bort 5V zener (D5).

- Den lilla 100pF kondensatorn (C4) flyttas bredvid PIC på målkretsen.

- Lysdioder tar ström från kretskortet där det är möjligt.

- MCLR uppdragningsmotstånd (R10) och diod (D10) krävs på målkretsen.

- VARNING. Målkortet måste ha en "flytande" strömförsörjning, helst ett batteri.

- Anslut inte måljord (VSS) till dator/PC -jord genom att ansluta andra datorportar samtidigt som JDM.

Efter simulering av JDM1 blev problemet med lång laddningstid på C2 uppenbart. Efter att ha läst Fruttenboel verkar det som att C2 och Q1 har lagts till som en ändring av originalet. Jag kan inte tänka mig vad C2 och Q1 är avsedda att göra förutom att skapa problem. Så för JDM4 återgår vi till den äldre designen på Fruttenboel som är enkel och okomplicerad att förstå. D1 och D3/LED2 klämma MCLR mellan VSS och VDD+8V. Värdet på R1 reduceras till 3k3, bara tillräckligt för att lysa upp LED2 vid 12V.

JDM4 är också utformad för att fungera med svagare seriella portar. När TX går högt (+9V), TX strömkälla = (9-8)/(1k +3k3) = 0,2ma, precis tillräckligt för att dra MCLR högt men otillräckligt för att lysa LED2. När TX blir låg (cirka -7V) sjunker TX -ström = (9-7)/1k = 2mA. LED1 ström = (7-2 för led)/(2k7) = 1,8mA. MCLR dra ner ström = 7-5,5/3k3 = 0,5mA.

Denna krets har också testats (JDM5-simulering) för att se vad som händer med seriella portar +/- 7V minimum, där det inte finns tillräcklig spänning för att upprätthålla VHH = 13V. Syftet med C1 blir nu uppenbart, C1 skapar en kort +ve boost till MCLR, en 33us spik på TX: s stigande kant, tillräckligt lång nog för att PIC kan komma in i programmeringsläge, kanske? Men ta bort bygel X2 (inaktivera LED1) eftersom det inte finns tillräckligt med ström för att dra MCLR lågt och tända LED1 tillsammans. När TX går lågt sjunker TX-ström = (7V-5.5V)/(1k+3k3) = 0.3mA, bara tillräckligt för att dra MCLR lågt mot pull-up R10.

Steg 7: Simuleringsresultat

För att se grafikfilerna är det bättre att högerklicka på länkarna nedan och sedan välja "Öppna länk i ny flik"

Simulering 1: spår av MCLR, VSS och RTS för original JDM1. Omedelbar observation 1, 2 och 3 är uppenbara.

Simulering 2: spår av MCLR och VSS och RTS för modifierad JDM2, som åtgärdar tidigare problem.

Simulering 3: spår av PGD, VSS och PGC för JDM2 som skickar data i programläge. Observation 4 vid 3,5 ms.

Simulering 4: spår av PGD, VSS och CTS för JDM2 i verifieringsläge (bygel X1 isatt). OK

Simulering 5: spår av MCLR, VSS, PGD och PGC för JDM3. ICSP som använder ström från krets löser många problem.

Simulering 6: spår av MCLR, VSS, PGD och PGC för JDM4 med +/- 9V seriell port. MCLR stiger omedelbart och fungerar fullt ut.

Simulering 7: spår av MCLR, VSS och TX för JDM5 med +/- 7V seriell port och bygel X2 borttagen. C1 skapar en +ve boost (spik) på stigande kant av MCLR, nästan tillräckligt för att skjuta MCLR över TX till 13V.

Steg 8: Slutsatser

Spice är riktigt bra på att avslöja "dolda hemligheter" för kretsdrift. Uppenbarligen fungerar JDM -kretsen och är kompatibel med många PIC -chips, men följande observationer avslöjar möjliga begränsningar/kompatibilitetsproblem/fel?

- Lång stigningstid för MCLR medan C2 laddas till VPP på TX: s första puls. Misslyckas specifikation 3.

- Seriell port laddar C2 när TX går högt och RTS går lågt. Men RTS har också jobbet att ladda C3. När båda inträffar samtidigt skapar detta mer belastning på RTS, följaktligen förlorar C3 laddning (VSS stiger) vid 2 ms vid simulering. Misslyckas specifikation 1.

- C3 tappar laddning (VSS börjar stiga) efter att klockpulserna stannat vid 3,5 ms.

- Vad är syftet med C2, behövs det alls?

Lösningar

- Förmodligen använder PICPgm en programvara "work-round". Den måste applicera en lång TX -puls för att förladdas till C2 och sedan bara gå in i programmeringsläget efter den andra TX -pulsen? För simulering minskade jag värdet av C2 till 1uF för att ge en stigningstid på 1 ms. Inte en idealisk lösning.

- Dela C2 och C3 så att de laddar oberoende. En liten ändring av JDM2, C2 refereras till GND istället för VSS.

- Löst av JDM3. ICSP är mycket mer tillförlitlig eftersom PIC drivs av målkrets.

- JDM4 löser problem 1. Detta är en enkel design som eliminerar C2 helt.

Steg 9: Och slutligen

Beviset på puddingen ligger i ätandet. Denna JDM fungerar så fortsätt använda den.

Och mina rekommendationer är:

- använd JDM2 för in -socket programmering och 12V seriella portar,

- använd JDM4 för ICSP-programmerare och seriella portar över +/- 9V,

- använd JDM4 med bygel X2 borttagen för seriella portar över +/- 7V.

Referenser:

Analog Devices LT -krydda

picpgm

Fruttenboel

Följ fler PIC-projekt i sly-corner

Rekommenderad:

Elegoo Super Started Kit Uno R3 Review: 4 steg

Elegoo Super Started Kit Uno R3 Recension: För några dagar sedan skickade Elegoo mig detta Super Starter Kit för testning. Så, låt oss se vad som finns inuti. När vi öppnar det här kompakta fodralet kan vi se massor av saker. På omslaget finns ett index med alla komponenter. Inuti har vi ett tackkort med alla

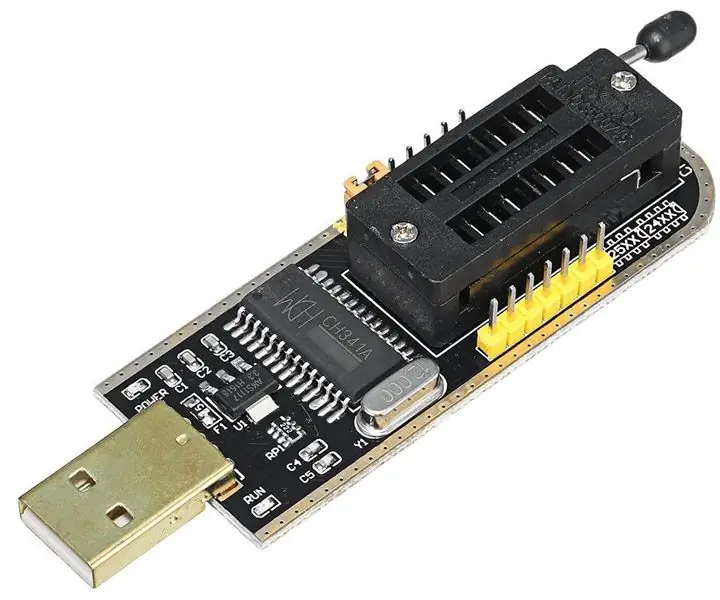

CH341A programmerare: 8 steg

CH341A programmerare: Jag har nyligen köpt en CH341A miniprogrammerare. Miniprogrammeraren är OK och kan användas för att programmera chips i 24 och 24 serier. Det är mycket lågt men ganska användbart eftersom jag kan använda det för att blinka min dator BIOS och routerns firmware.WCH har vänligen släppt

Arduino Som ISP -- Bränn hexfil i AVR -- Säkring i AVR -- Arduino som programmerare: 10 steg

Arduino Som ISP || Bränn hexfil i AVR || Säkring i AVR || Arduino som programmerare: ……………………… Prenumerera på min YouTube -kanal för fler videor …….. Denna artikel handlar om arduino som isp. Om du vill ladda upp hex -fil eller om du vill ställa in din säkring i AVR behöver du inte köpa en programmerare, du kan göra

Hur man flashar eller programmerar ESP8266 AT -firmware med hjälp av ESP8266 blinkare och programmerare, IOT Wifi -modul: 6 steg

Hur man flashar eller programmerar ESP8266 AT-firmware med hjälp av ESP8266 blinkare och programmerare, IOT Wifi-modul: Beskrivning: Denna modul är en USB-adapter /programmerare för ESP8266-moduler av typen ESP-01 eller ESP-01S. Den är bekvämt utrustad med en 2x4P 2.54mm hona för att ansluta ESP01. Det bryter också ut alla stiften på ESP-01 via en 2x4P 2,54 mm hane

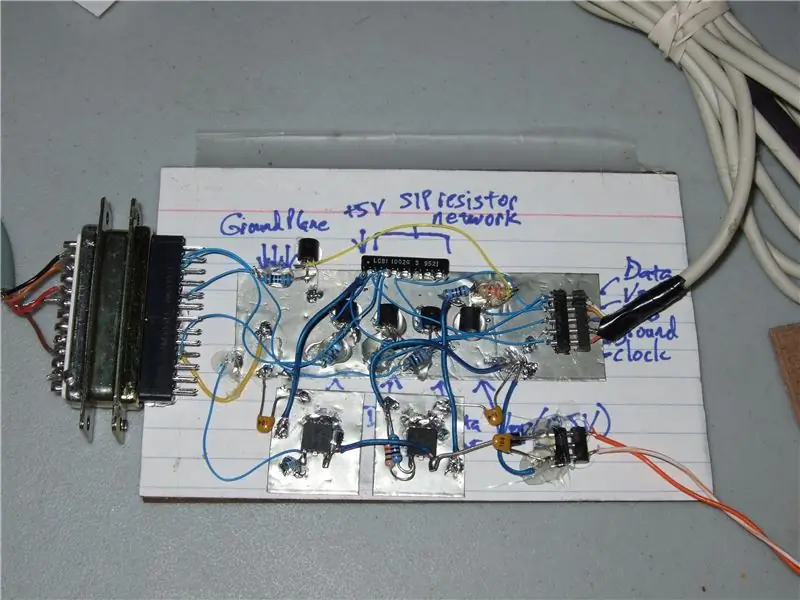

5 Transistor PIC -programmerare *Schematisk tillagd till steg 9 !: 9 steg

5 Transistor PIC -programmerare *Schematisk tillagd till steg 9 !: Gör din egen PIC -programmerare för datorns parallellport. Detta är en variant av David Taits klassiska design. Det är mycket tillförlitligt och det finns bra programmeringsprogramvara gratis. Jag gillar IC-Prog och PICpgm programmerare. Bäst av allt, det